プロセスの名称にもなった

バイポーラ

TTL ICをもっと大規模にしたものが、バイポーラと呼ばれるものである。これには語弊があり、バイポーラというのは後述するFETと対比的に使われる用語で、単なるトランジスタを指している。ただFETもトランジスタの一種であって、これを区別するために、ここまで説明してきたトランジスタのことをバイポーラトランジスタと呼んでいる。

このバイポーラがそのままプロセスの名称として使われているわけだ。バイポーラベースのデジタル回路を高速に動作させるECL(Emitter Coupled Logic)という技法と組み合わせることがほとんどどであるが、このECLは80年代前半のメインフレーム用のCPUには広く使われていた。

ワークステーション用としては、MIPSの「R6000」が完全にECLで製造されている。この後説明するCMOSとバイポーラを組み合わせたBiCMOSは、インテルの「Pentium」でも利用されていた。なおBiCMOSは、性能に直結する部分をバイポーラ/ECLで作成し、その他をCMOSで作成するハイブリッド方式である。

最後にこのバイポーラ/ECLを使った製品は、Exponential Technologyの「x704」というPowerPC互換チップではなかろうか。「x704」はBiCMOSといいつつ、CPUのほとんどどがECLで構成された製品で、当時CMOSで製造された「PowerPC 604e」が250MHz程度の動作速度までしか上げられなかったのに対し、x704は533MHz動作が可能という高速性をウリにした製品であった。

もっとも233MHz動作の「PowerPC 604e」が18W程度の消費電力だったのに対し、「x704」は533MHz動作で85Wに達しており、これが理由で最終製品への採用例は皆無だった。

バイポーラがデジタル回路向けに廃れた理由は、その消費電力の大きさにある。もう一度トランジスタに話を戻すと、原理的に値が1の時には電流が流れっぱなしになる。つまり値が1なら、その間流れる電流が最終的に全部熱の形で消費電力として消えることになる。言うまでもなくこれは発熱の観点から非常に問題であり、これがバイポーラ/ECLがCMOSに置き換えられた最大の理由である。

少ない消費電力で回路を作れる

FET(電界効果トランジスタ)

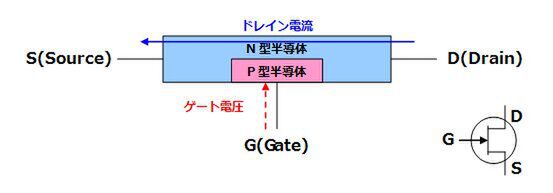

トランジスタからやや遅れて登場したのがFET(Field Effect Transistor:電界効果トランジスタ)と呼ばれるものである。 FETには色々なタイプがあるが、下図は基本的な接合型FETと呼ばれるものの構造を、さらに単純化したものである。

接合型FETを単純化したもの。これはN型FETと呼ばれるが、N型半導体とP型半導体を逆にしたP型FETも存在する

トランジスタの場合、ベース電流に比例する形でエミッター電流が流れるというものだったが、FETの場合は「ゲート電圧に反比例※2する形で、ドレイン電流が流れる」という動き方をする。

※2:正確には反比例ではなく、「電圧が0だと自由にドレイン電流が流れるが、電圧をかけていくと次第にドレイン電流が減り、ある程度以上だと0になる」だけで、その関係がきっちり反比例になるとは限らない。

つまりトランジスタでは電流を流しっぱなしにしないと「1」にならないが、FETを使うと電圧をかけさえすれば、電流そのものはずっと少なくて構わない。この結果として、バイポーラ/ECLに比べると少ない消費電力で同じ回路を実現できるのが、FETのメリットである。

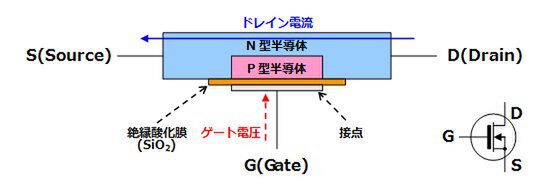

さて、このFETをもう一段進めたのがMOSFETである。MOSというのはMetal Oxide Semiconductorの略で、日本語では金属酸化膜半導体と称する。構造は下図のようになっており、Gateが直接P型半導体に接続されるのではなく、間にSiO2(シリコン酸化物)の絶縁層を挟んだ形になる。

MOSFETの構造

この酸化膜を挟んだ結果として、ゲートの接点とP型半導体の間にはコンデンサーが形成されることになる。するとなにがよくなるかというと、FETの動きが先ほどとひっくり返るのである。

つまりゲート電圧をかけない状態では、ドレイン電流が一切流れなくなる。そしてゲート電圧を掛けてゆくと、次第にドレイン電流が流れ始め、ある程度の電圧で最大になる形だ。

要は「なにもしないときには、なにも流れない」ということで、これはロジック回路などを構成するのに非常に都合がよい。そこで、80年代からこのMOSFETを使ってICを作るようになってきた。

例えばインテルが1982年に発売した「80286」はHMOS-III(NMOSのインテル社内での名称)で製造されている。ただその「80286」も、後にはCMOSに切り替わった。

ではそのCMOS(Complementary MOS:相補型MOS)とはどういうものだろうか。次ページで解説しよう。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ