大規模な検証とデバッグには

専用のボードを使用する

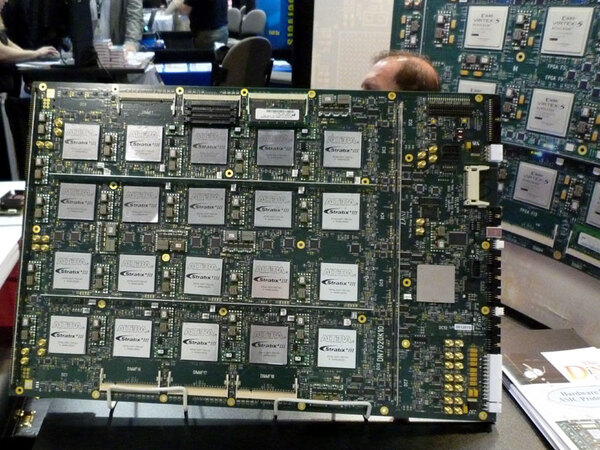

では、検証をどうやってやるかだが、極めて小規模な回路レベルであれば、ソフトウェアのシミュレーターで確認できる。ただある程度の規模になると、当然ながらソフトウェアシミュレーションでは到底間に合わない。そこで登場するのが下の写真のボードである。

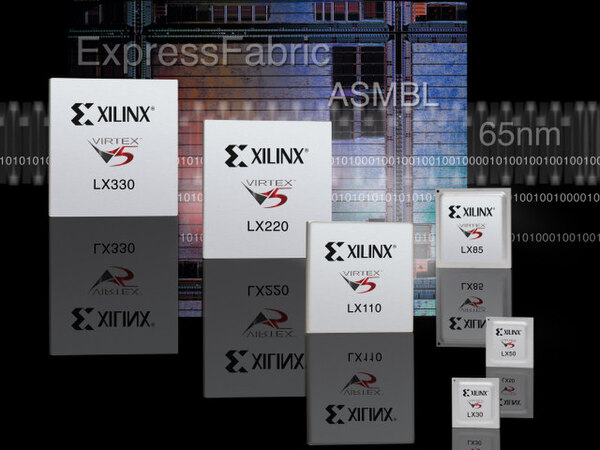

このボードは、2009年当時にAlteraで最大容量を誇った「Startix III FPGA」を20個搭載したボードである。背後に見えるボードは、Xilinxの「Virtex-5 FPGA」をやはり多数搭載したもので、そのベンダーの趣味やそれまでの開発リソースに応じてどちらのボードでも提供できるようにしているわけだ。

FPGAというものは連載229回に名前が出てきたが、ハードウェアの回路をソフトウェア的に組み込んで実行できるデバイスである。

このFPGAに、まずはブロック単位で論理設計が終わった部分を流し込み、ついでにその前後にテスト用の回路などもやはり論理設計を行なって単体で動作させて、テストするというわけだ。

ちなみに、FPGAは同じプロセスで製造されたASICに比べて10倍ほど効率が悪い。ここで言う効率とは論理回路数/トランジスタ数比であって、例えばASICだとトランジスタ10個で組める回路が、FPGAにすると100個必要になるという意味である。

このため、メモリーコントローラーのような小規模な回路なら1個のFPGAで収まるが、ある程度大きくなると到底1個のFPGAに収まらない。そのため、このようなお化けボードを場合によっては複数枚用意し、論理回路の側は複数のFPGAに収まるように適時分割して収めるわけだ。

もちろん、これでは動作速度がなかなか上がらないが、フルスピードで動かすとテストが間に合わないため、もともとフルスピードでは動作させない。テストやデバッグ用の回路なども追加した状態でFPGAに入れるのが普通なので、速度はそれなりである。

それなり、というのは最初は本当に数Hzで、場合によってはステップ動作での動作検証になるため、速度云々はまったく問題にならない。ある程度動くようになったら、例えばCPUだとLinux Kernelを流してみることになるのだが、その時点でもまだ数十MHzが普通であって、100MHzも動けば十分ということになる。

余談になるが、このFPGA。AlteraにしてもXilinxにしても、ある程度の数(数万個程度)をまとめて発注すると大分価格が下がるが、逆に1個や10個で発注をかけると、特にハイエンド品は猛烈な価格になってくる。

前述のボード写真に出ている「Virtex-5」のハイエンド品は1個100万円なのだが、現在のXilinxのハイエンドである「Virtex-7 2000T」では1個400万円という価格がついている。

この手のボードだとある程度まとめてFPGAを購入するからもうすこし部品原価は下がるだろうが、それでも1枚あたり数百万~1千万円超になっても不思議ではない。SoCベンダーの開発室に行くと、この手のボードがごろごろ転がっているのは「よくある風景」だ。

結合テストはシミュレーションで行なう

FPGAに論理回路を分割して入れる手間はばかにならない。そのうえ、ある程度テストが進んで複数のコンポーネントをバスでつないで連携動作というタイミングになってくると、「遅い時には問題なく動くのだが、速度を上げると動かなくなる」という問題が必ず出てくる。

このレベルの結合テストで長らく利用されてきているのがシミュレーションである。要するにソフトウェア上でハードウェアを完全にシミュレーションするのである。

例えば1GHzで動作するSoCであれば、カウンターを1マイクロ秒づつ進めながら、その際に個々の回路やトランジスターがどう動くかを回路全体に対して計算するという恐ろしく手間のかかる作業である。

すでに元の文献がないので記憶違いの可能性もあるが、大昔にインテルが「80386」を開発していたとき、IBMの「3090」というメインフレームを使ってシミュレーションを走らせ、電源投入からMS-DOSのプロンプトが出るまでの動作に実時間で3日かかったという話があった。

速度そのものは、その後のプロセッサーの進歩によってどんどん高速化していったが、その一方でLSIそのものの規模もどんどん大きくなっているため、結局のところ時間がかかることには変わりがない。

先の例では、「80386」が27.5万個のトランジスターで構築されているが、昨今のSoCは28nmプロセスを使うものだと大体10億個近くになっており、回路規模は4000倍ほどになる。

一方、性能比は「80386」が33MHz動作で11.4MIPS、対して最近のプロセッサーは、例えばインテルの「Core i7-3960X」が3.33GHz動作で17万7300MIPSなので1万5500倍ほどになる。

つまり1985年当時に比べると3倍ほど効率が良くなっている可能性があるが、これは電源を入れてからDOSプロンプトが出るまで3日だったのが1日に減った程度で、まだ十分とは言えない。

そこでEDAベンダーからはハードウェアアクセラレーターというものが提供されている。これは回路シミュレーションに特化した専用回路を搭載した巨大な箱で、EDAツールを動かすワークステーションに接続して使うものだ。

これを利用すると、論理回路のシミュレーション速度が、ワークステーション単体で行なった場合に比べて数万倍から数十万倍になるとされる。

下の写真はEDAベンダーの大手の1つであるCadenceの「Palladium」シリーズのアクセラレーターの外観であるが、以前AMDやインテルの後工程工場の中のテスト工程を見学した際に、これらがごろごろと転がっていた。

ちなみに価格は、設計ツールとの組み合わせなので単体価格は提示されないが、ローエンドのものですら数億円、メインに使うグレードのものだと数十億円である。もっともEDAツールそのものが上から下まで全部そろえると数十億円の世界なため、極端に高いとも言いがたい。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ