出来合いの回路つまり

IPの利用

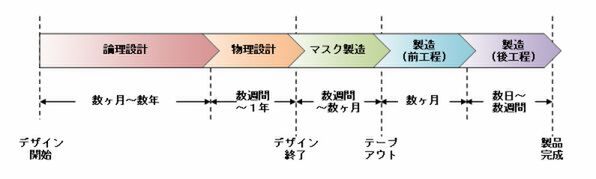

通り一遍を説明するだけでこれだけの手間がかかっているわけで、新規に作り始める場合、図2で言うデザイン開始から製品完成まで、下手をすると5年以上かかることになる。

もちろん新アーキテクチャーのCPUならこの位かかるのは普通で、すでにある製品を継続投入しながら次第に新製品をオーバーラップさせてゆく方法での商品展開が可能ならば、これはありえる。

しかし、携帯電話向けプロセッサーのように短い期間で製品ラインナップが入れ替わるようなケースでは、そんな悠長なことはしてられない。そこで広く利用されているのがIPである。

IPはIntellectual Propertyの略で、日本語にすると「知的財産権」なんて翻訳があたっているがあるが、これはIP違い。この知的財産権とは、特許権や実用新案権、著作権や商標権といった権利の総称であって、英語ではやはりIntellectual Propertyの用語が使われているのだが、半導体の現場でのIPとはやや異なる。混乱を招かないようにということでか、最近はIP Coreなんて言い方をする場合もある。

では半導体の現場におけるIPとはなんであろうか。言ってみれば「出来合いの回路」の意味である。

ARMやImagination Technologyがその最右翼で、CortexシリーズやMIPSシリーズといったCPUコアや、Mali GPUやPowerVR)などのGPUコアだけでなく、メモリーコントローラー、内部バス、SoC内部のインターコネクト、USB、SATA、MMC/SDIO、SPI/I2Cといった各種周辺I/Oなど、世の中には多様多種のIPが満ち溢れており、これを使うことで設計期間を短縮できる。

論理設計レベルのSoft IPと

実体配線レベルのHard IP

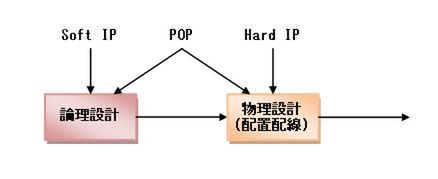

このIPにも2種類存在する。通常Soft IP(Soft Core)と呼ばれているものと、Hard IP(Hard Core)と呼ばれているものだ。Soft IPは論理設計レベルで利用できるもので、ARMのCortex-Aシリーズは通常このSoft IPが利用される。

これにより設計者は、CPUの構成とかに頭を悩ませる必要はなく、せいぜいが2次キャッシュの容量をどの位にするか、TLBのサイズをどの程度にするかといった、Soft IPのパラメーターを定めるだけである。

全体の開発期間から言えば論理設計の部分が一番長いだけに、ここに出来合いの部品を使えばその分の開発期間が短縮できることになる。

スマートフォンやタブレット向けのSoCを作るのであれば、例えば「CPUコアはARMのCortex-Aシリーズにしてほしい。そうすればCortex-A向けのアプリケーションが全部使える」とか、「グラフィックはPowerVRにしてほしい」など、マーケティング的要因で主要なコンポーネントの選択は決まってしまう。

ここで無理に「Cortex-A15互換の命令セットを持つCPUコアを新規に作る」と無理をするよりは、素直にARMからCPUのSoft IPを購入して組み込んだ方がトータルとしてエンジニアリングコスト節約や開発期間の短縮につながる。むしろエンジニアリングコストは、CPUコアやGPUコア以外の部分に注力して、そこで差別化する方が効果的というわけだ。

ただ、Soft IPを組み込んでも物理設計の時間は短縮できない。Soft IPはあくまで論理設計レベルの回路図で、物理設計をするのは開発者の仕事である。

この手間をさらに省き、物理設計まで終わった段階での回路図、というより実体配線図レベルのものを提供するのがHard IPである。これなら当然その分の物理設計は不要になるため、さらに開発期間が短縮できる。

ただし当たり前ではあるが、物理設計は実際に利用するファウンダリーの、特定のプロセスに特化したものになる。例えばTSMCの90nm Gプロセス向けのHard IPを、TSMCの65nm LPプロセスには使えないわけで(両者は物理レベルでは完全に別物である)、従ってファンダリー/プロセス毎に別々のHard IPが必要になる。

実はこれが理由で、ARMやMIPSなどの主要なIPベンダーは一時期Hard IPを提供せず、Soft IPのみを提供していた。ところが最近になって、特に先端プロセスではこの物理設計の難易度が上がったことで、再びHard IPのニーズが増えてきている。

ARMは先端プロセスに関し、ファンダリーおよびEDA(Electronic Design Automation:論理/物理設計システム)のベンダーと共同でHard IPを開発、これを提供するという形を取っている。

これにあわせて最近ARMが力を入れているのがPOP(Processor Optimization Package)と呼ばれているIPである。POPはARMの独自の用語であるが、位置づけとしてはSoft IPとHard IPのちょうど中間に位置する。

Hard IPほどにはガチガチに構成が決まっていないものの、特定のファウンダリー/プロセスに向けてある程度最適化が済んだSoft IPといえば理解しやすいだろうか。

こうしたものを利用することで、設計者は論理設計と物理設計の時間を最小化してSoCを作れるようになっている、というのが昨今の動向である。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ