Quarkの中身はPentiumコア

今後はAtomベースになる可能性大

「Quark X1000」の仕様を簡単に列挙すると以下の通りだ。

- X1000はQuarkファミリーの最初のシリコン。つまりまだ後継製品が出る可能性アリ。

- X1000はSoC構成。CPUコアのみならず周辺回路まで全部搭載している。

- ダイサイズはおおよそAtomの5分の1。ただしダイサイズというよりもエリアサイズの可能性あり。

- 消費電力はAtomの約10分の1。ただこれも「何の」消費電力かは未定。SoC全体としては、400MHz駆動の製品のTDPが1.9W~2.2Wとされる。

- すでにリファレンスデザインを用意しており、特定顧客への提供も始まっている。一般向けとしては、Galileoボードがまもなく登場予定。

- コアはFull-Synthesizable。つまりインテル以外のファウンダリーを使っての製造も理論上は可能。

- CPUコアはPentiumのものを利用。

- オンダイで512KBのSRAMを搭載。

- 外部に16bit/800MHzのDDR3 I/Fを搭載。

- 周辺回路としてPCIe Gen2 ×1、USB×2、10/100BASE-T Mac、SDIO、UART×2、SPI×3(うち一つはLSPI対応)、I2C、GPIOを搭載。

これらについて、もう少し説明しておく。Quarkシリーズに利用されるCPUコアに関してRani N. Borkar氏(Vice President, General Manager, Intel Architecture Development Group)は「Atomグループの一種」という漠然とした説明を行なった。

その一方で、Galileoボードのドキュメントには、“400MHz 32-bit Intel Pentium instruction set architecture (ISA)-compatible processor”(400MHz駆動となる、Pentiumと互換の命令セットをサポートした32bitプロセッサー)と説明があり、これは完全に矛盾している。

Pentium互換というのは、要するに64bit拡張は元より、Pentium Pro以降に搭載された拡張命令類まで全部未サポートという意味である。一方、AtomはSSSE3までサポートしており、その意味ではMerom世代のCore 2との互換性がある。もしQuark X1000が本当にAtomベースであれば、これらの拡張命令を無効にする意味がまったくない。しかし、これはBorkar氏の説明と合わない。

実体としては、Quark X1000そのものはAtomとは無関係の、Pentiumコアをそのまま持ってきたものである。ただしインテルはこのQuarkの将来製品を予定しており、こちらはAtomベースに切り替わる可能性が高い。だからこそBorkar氏は非常にぼかした説明を行なったと考えるのが正しいだろう。

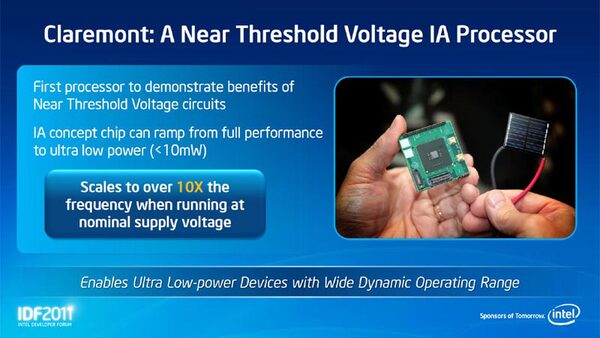

ではなぜPentiumなのかというと、元となるClaremontというCPUコアをインテルは2012年に発表しているからだ。これは製品ではなく、インテルのR&D部門が開発し、2012年にISSCC(International Solid-State Circuits Conference)という学会で発表をしたものである。

このClaremontは、Pentiumのコアをベースに、NTV(Near Threshold Voltage)という技術を使うことで、3MHz@0.28V~915MHz@1.2Vという広い動作周波数/電圧範囲で動作できることを実証している。

インテルのR&DチームはどうもPentiumが好きらしくて、なにかというとPentiumを持ち出してきて実装する。現在の「Xeon Phi」も、ベースとなるのはやはりPentiumだったわけで、インテルにとってはどうもPentiumのコアは使いまわしをするのに手頃なものなようだ。

ただし、Claremontそのものは純粋にCPUコアだけで、このままではIoT向きでもなんでもないので、色々周辺回路を追加する必要がある。こうして作られたのがQuark X1000であろう、というのは筆者の想像であるが、そう外れていない気がする。

ちなみに消費電力がAtomの10分の1というのは、おそらくCPUコアだけであろう。Claremontの場合、3MHz@0.28Vにおける消費電力は2mW、915MHz@1.2Vの場合は737mWと発表されている。今回の場合、動作周波数は400MHz程度なので、コア電圧は1Vを多少下回る程度と見られる。 消費電力は不明だが、200mWは無理にしても400mWを下回る程度になっても不思議ではない。その意味では、CPUコア単体で2W近い初代Atomと比較すると、コアの消費電力そのものが10分の1というのは、そう無茶な数字ではない。

同様にClaremontの発表時のコアのエリアサイズ(CPUコア+1次キャッシュのみの面積)は1.1mm×1.8mmでほぼ2mm2と発表されている。

初代のAtomが大体25mm2のダイサイズだが、半分以上を2次キャッシュとI/Oパッドが占めていることを考えると、純粋なCPUコアのエリアサイズは10mm2程度で、こちらは綺麗に5分の1になる。Claremontをそのまま流用したと考えると、諸々の数字が綺麗に合うあたりは。やはりClearemonベースであろう、という傍証になる。

次のFull-Synthesizableについては、これもClaremontがそもそもFull-Synthesizableだったから、それをそのまま継承したと考えるのが妥当だろう。

ちなみにFull-Synthesizableというのは「どこのファウンダリーに持っていっても製造できる」という意味に捉えてもらうのが正しい。インテルはこれまで、自社の製造プロセスに最適化する形で回路設計を行なっていたから、まったくFull-Synthesizableではなかった。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ