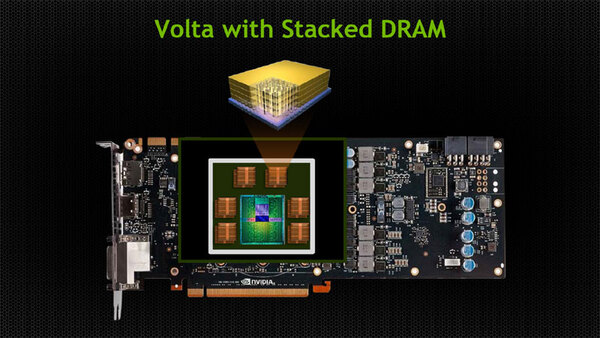

独自のStacked DRAMを採用する

「Volta」

Maxwellの後にはVoltaが控えている。しかし、このVoltaはさらに難しい。Voltaでは今のところHMC(Hybrid Memory Cube)を使う予定がなく、独自のStacked DRAMを使うとしている。これは、最高速であるGDDR5の7Gbps品をすでに使ってしまっており、この先速度の向上がまったく望めないため、Voltaの世代ではGDDRを捨てて独自の規格にしたということである。

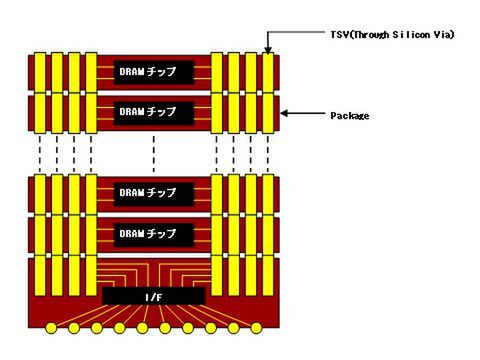

構造的にはHMCと似ており、下図のように複数のDRAMチップを縦方向に積層、一番下にI/Fがあるという構造だ。このDRAMチップ同士とI/Fを繋ぐのがTSV(Through Silicon Via:シリコン貫通ビア)と呼ばれるもので、現在ファウンダリー各社や独立系の半導体メーカーが実現を急いでいる。

Volta独自のStacked DRAM構造

試作のレベルでは色々製品もあり、きわめて限られた用途では実用にもなっているのだが、現時点では量産のレベルに至っておらず、またコストの面でもかなり高価になることが予想されている。

実のところ価格は卵と鶏の関係にあるので、どこかが量産に入らない限りなかなか下がらない。逆に言えば、誰かがエイヤッと始めると、急激に下がる可能性もあるのだが、Voltaはこの独自Stacked DRAMを使う前提で開発が進んでいる関係で、2014年中は難しいと見られているためだ。

TSMCもTSVの実用化に向けて開発を進めているが、今のところTSVが利用可能になる時期を明示していない。TSVそのものはCoWoS(Chip on Wafer on Substrate)で利用できる(関連リンク)ことをアナウンスしているが、これは上図のように複数チップをどんどん積み上げるものでなく、1つのチップとシリコンで作られた補助基板(Substrate)の間のみをTSVで繋ぐという限られた用途向けだからだ。

TSMCは学会などではTSVの実用化に向けた様々な研究成果を発表し続けているが、まだそういう段階という言い方もできる。2014年中に量産試作が出来るかどうかも怪しく、現実問題としては2015年以降になるだろう、というのが一般的な見方とされている。したがってTSMCのTSV技術をベースとするVoltaのStacked DRAMの登場時期も2015年以降となるだろう。

幸いにもMaxwellの場合、2014年中には製造技術を16nm FinFETにアップデートできる可能性が高い。16nm FinFETの場合、配線層そのものは20nmプロセスのものをそのまま使い、トランジスターのみFinFETに入れ替えることになる。つまり回路規模を大きくするとダイサイズがそのまま増えるため、回路密度そのものは変わらないまま、動作速度の向上や消費電力の低減が期待できるので、これでもう一段性能を改善できる。

個人的には、先に述べたGM100かGM110かわからないが、GPGPU向けのダイは、20nmプロセス世代をスキップして16nmプロセス世代で投入されるのではないかという気がしているが、残念ながらこのあたりはまだ確たる情報が存在しない。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ