22nmプロセスに微細化

内部アーキテクチャーも一新

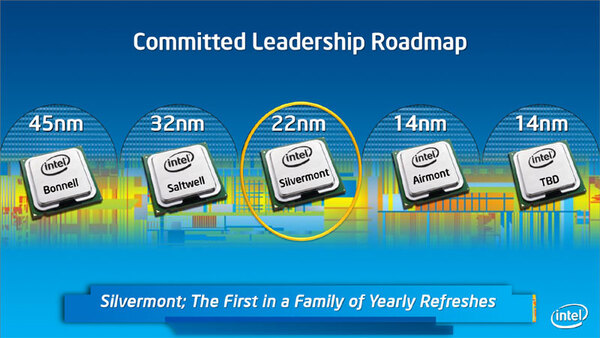

製品の位置付けの話はこのくらいにして、ロードマップの話をしよう。Silvermontは、Atomシリーズとしては久しぶりのリフレッシュになっている。

もともとAtomの場合、Tick-Tock戦略にうまくはまらなかったため、45nmのBonnellが2008年に登場してから昨年32nmのSaltwellが投入されるまで4年以上も経過することになってしまった。ただBonnellとSaltwellはプロセスはともかく内部構造は完全に同一で、その意味ではここがTickにあたる。

今回はプロセスに加えて内部アーキテクチャーも一新しているので、TickとTockの両方ということになる。ただこれまで言われてきたTick-Tockは基本的にはPentium M以降のパイプラインを少しづつ改変しているレベルであり、マイクロアーキテクチャーを全部入れ替えたSilvermontの場合、例えるならNetBurstマイクロアーキテクチャーからCoreマイクロアーキテクチャーへの切り替えに近いレベルなので、Tockのレベルと言って良いかどうかは微妙だ。

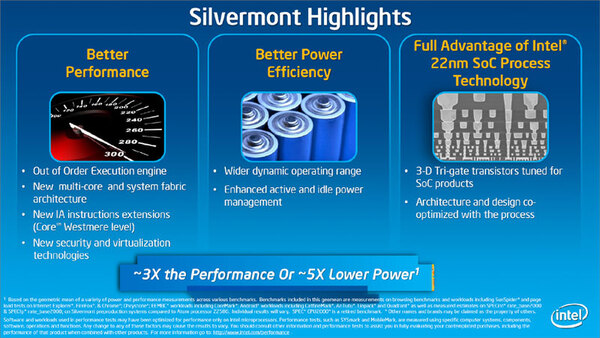

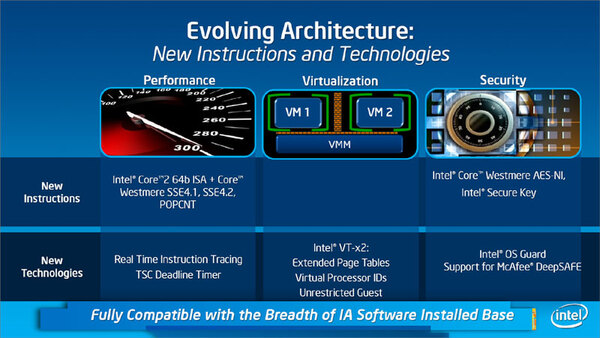

これに続いて、14nm世代ではAirmontが用意され、その後にもう一世代14nm製品が続くことが今回明らかにされたわけで、ここからはTick-Tockが復活するかもしれない。少なくともSilvermont→AirmontはTick、つまり内部構造は小変更に留め、プロセスの微細化を行なったものになりそうだ。そのSilvermontの主要な特徴が下の画像だ。

繰り返しになるが、Out-of-Orderの実行ユニットと、Westmere(SandyBridgeの1つ前のCore iシリーズ)相当の命令拡張、それと新しいセキュリティ/仮想化技術を搭載し、22nm SoCプロセスで製造され、幅広い動作周波数レンジでの動作をカバーするとしている。

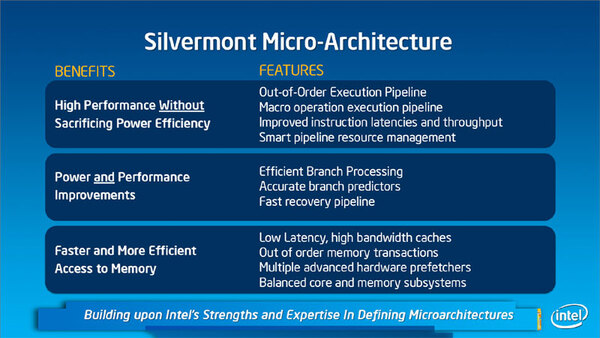

まずマイクロアーキテクチャーは、Macro FusionをサポートするOut-of-Orderであることが示されており、最低でも2命令同時実行がサポートされていると思われる。また分岐予測の改善やパイプラインリカバー(パイプラインハザードから高速に復帰する)などとあるため、パイプライン段数は結構少なめかもしれない。

さらに、実行パイプラインのみならずメモリーアクセスに関してもOut-of-Orderが実装されることが示された。ただこのメモリーアクセスのOut-of-Order化は、CPUコア側というよりはシステムエージェント側の機能のようだ。

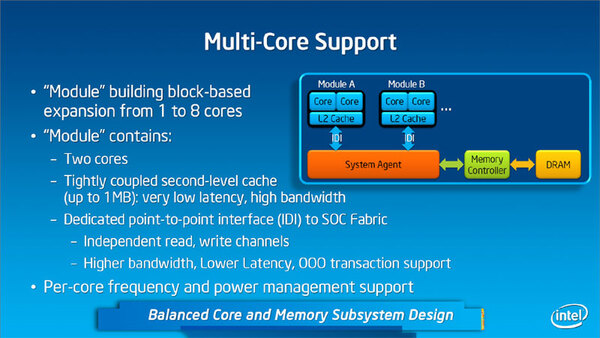

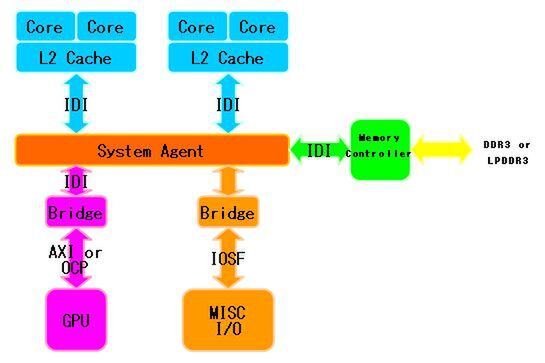

下の画像は、そぼシステムエージェントとの構成である。

これには、以下のような特徴が示されている。

- CPUは2コア+2次共有キャッシュ(最大1MB)で1つのモジュールを構成する

- 各々のモジュールは、IDIと呼ばれる独立バスでシステムエージェントモジュールと接続される。このIDIはリード(システムエージェント→コア)とライト(コア→システムエージェント)が分離されたバスとなる

- システムエージェントはファブリックで構成され、リード/ライトの要求をOut-of-Orderで実行できる

- 動作周波数及び電源は(モジュール単位ではなく)コア単位で管理される

これを使うと、システムがどんな具合に構成されるかを推定したのが下図である。

Silvermontにおけるシステム構成の推定図

これはスマートフォン向けの例だが、2ないし4コアのCPUに加えて、GPUやさまざまな周辺I/Oとメモリーコントローラーが、全部システムエージェントにつながる形となると思われる。このシステムエージェント自体はあくまでIDIでのみ管理を行なっており、GPUコアや周辺回路はブリッジを経由する形で、AXI/OCPやIOSFで接続される様になるのではないかと想像する。なお、AXI/OCP/IOSFについては連載173回を参照してもらいたい。

コアに話を戻すと、拡張命令に関しては下の画像のようになっている。要するにSandy Bridgeで導入されたAVX命令こそ搭載されていないが、それ以前のWestmere世代までに搭載された拡張命令系はすべてサポートする。このあたり、いち早くAVX命令を導入したAMDのJaguarコアとの対比が面白いところだ。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ