ネットワーク仮想化を加速する「StrataXGS Trident II」

VXLANもNVGREもワイヤレートで!ブロードコムの新ASIC

2012年09月11日 07時00分更新

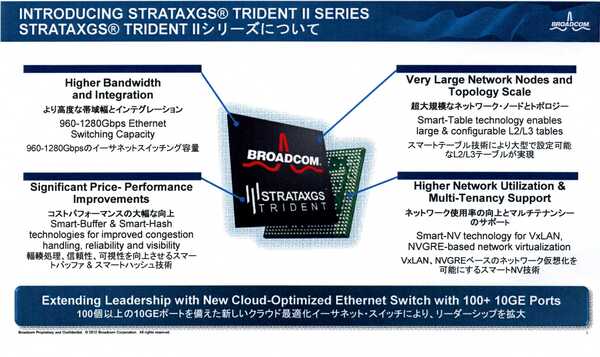

9月10日、ブロードコムは新Ethernetスイッチングソリューション「StrataXGS Trident IIシリーズ」を発表した。米国本社では8月27日に発表済みの製品で、シングルチップで100以上の10GbEポートをサポートできる世界初の製品だという。また、ネットワーク仮想化に使われる主要プロトコルをチップレベルで高速化できる機能も実装される。

40GbEを最大32ポート実現する高集積化

StrataXGS Trident IIシリーズは10/40GbEスイッチの機能をワンチップでカバーする製品で、データ転送容量は前世代の2倍の1280Gbpsに向上している。この結果、全て10Gbpsポートの構成なら最大104ポート、全て40Gbpsポート構成なら最大32ポート、両者を混在させる場合は10Gbps×96+40Gbps×8や10Gbps×64+40Gbps×16といった構成が実現できる。

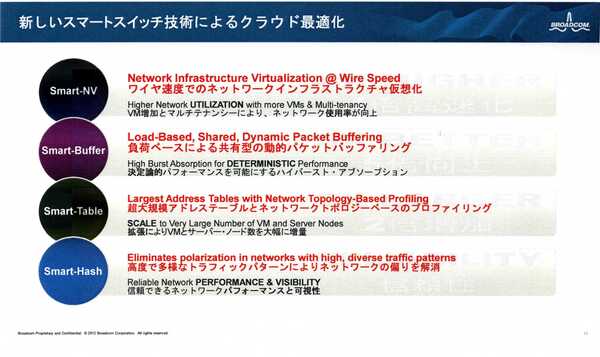

ネットワーク仮想化に対してハードウェアでの高速化機能を実装している点も特徴となる。Smart-NV機能では、ネットワーク仮想化のために利用されるトンネリングプロトコルであるVXLAN(VMwareやシスコが推進)とNVGRE(マイクロソフトがHyper-V 3.0でサポート)をサポートし、これらのトンネリングプロトコルを介した通信でもワイヤーレートでの通信を実現する。

説明を行なった米ブロードコムのインフラストラクチャ&ネットワーキンググループ(ING) プロダクトマーケティング ディレクターのスジャール・ダス氏はまず市場状況について説明を行なった。同氏は、「2012年から2016年に掛けて、データセンターの10GbEポート数は年平均40%増、40GbEポート数は年平均130%増」という予測を紹介し、40GbEスイッチの市場が急速に成長するとした。また同氏はネットワークの高速化の歴史を振り返り、100Mbps Ethernet(Fast Ethernet)や1Gbps Ethernetの時代にはまだスイッチベンダーごとのカスタムOEM ASICが中心だったが、10/40GbEの時代に入ると市販スイッチASICが中心になりつつあると指摘した。

その上で同氏は、同社のStrataXGS Tridentはまさにこうしたトレンドの中核に位置する市販ASICであり、「トップオブラックスイッチおよびアグリゲーションスイッチ市場において、サーバ市場におけるx86プロセッサと同様の役割を担うものだ」と語り、事実上の標準の地位を獲得したとの自負を見せた。同チップは現在サンプル出荷が開始されている段階だという。

なお、ネットワーク仮想化プロトコルとして最近注目を集めているNicira NetworksのSTT(Stateless Transport Tunneling)への対応について、ダス氏は「現時点では対応予定はない」と語った。その理由は技術的な問題で、STTをスイッチングハードウェア側で高速化しようとすると状態(State)を保持する必要があり、そのためにはチップ内にメモリ容量を確保する必要があるためだとしている。

消費電力を引き上げるメモリの増加を抑制

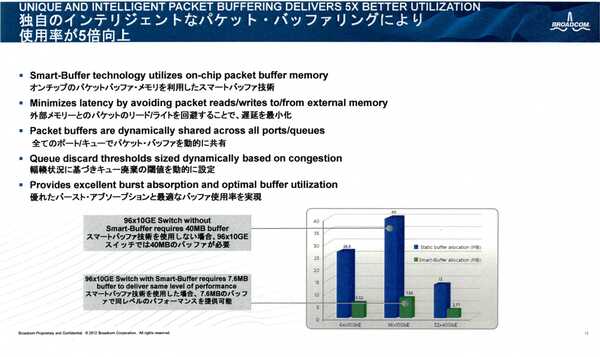

同社では、帯域幅/規模/機能性の向上を求めると同時にチップサイズ/システムコスト/消費電力は上げられないという市場の状況を強く意識しており、中でもチップサイズを増大させ、消費電力を引き上げるメモリ実装量の増加には大きな注意を払っているようだ。

このことは、チップ上のパケットバッファの利用効率を向上させるための「Smart-Buffer」機能をTrident IIに実装し、メモリ利用効率を従来比5倍に引き上げている点からも伺える。これは、従来はポートごとに静的に割り当てが行なわれていたパケットバッファを動的割り当てに変更するなどの工夫で実現している。10GbE×96ポート構成の例では、Smart-Bufferを使用しない場合のパケットバッファサイズは40MBなのに対し、Smart-Bufferを利用すると7.6MBに抑制されるという。StrataXGS Trident IIは前世代と同じ40nmプロセスで製造されているということだが、プロセスの微細化なしに2倍の帯域向上を実現した背景には、オンチップのメモリ量を増大させることなくパフォーマンスを向上させるためのさまざまな工夫があったことが分かる。