トランジスター数の増加が

CPUへの機能統合を生む

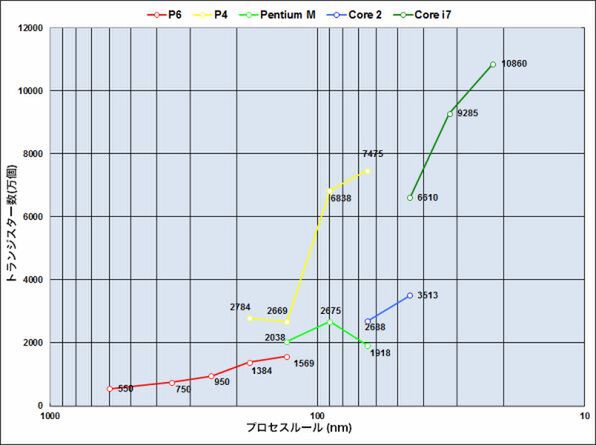

最後のグラフ5は、プロセスルールと1コアあたりのトランジスター数を試算したものだ。以下の式で、CPUコア+1次キャッシュのトランジスター数を算出している。ただし、ややラフな計算である。

- (総トランジスター数-GPUのトランジスター数(あれば)-2次/3次キャッシュのトランジスター数)÷コア数

Core 2の世代までは、この式でのトランジスター数計算は比較的簡単だった。しかしCore i世代になると、CPUコア以外の部分(Uncore部)であるPCI Expressやメモリーコントローラーの合計トランジスター数が不明である。仕方がないので、これらはコアの中に含めてしまっている。

また、Core iの第1世代は「Core i7-880」を使って算出している関係でGPUは必要がないが、第2世代の「Core i7-2700K」や第3世代の「Core i7-3770K」では、GPUの分を減算しないといけない。ところが、Core i7-2700KはGPU部分が1億1400万トランジスターと発表されているのだが、Core i7-3770Kでは未公表である。仕方がないので、「GPU性能がおおむね倍だから、トランジスター数は4倍程度だろう」と、大雑把に4億5600万トランジスターとして算出している。あくまで参考程度にしてほしい。

グラフ5からわかるのは、「Prescott」以降のPentium 4を除くと、最近のCPUコア+1次キャッシュは3千万トランジスター程度で実現できることだ。Core i7は上記の理由であまり信用できない数字だが、総トランジスター数の半分がUncore部とすると、1コアが3000万~5000万トランジスターといったあたりだ。デコーダを完全マイクロコードに置き換えたPrescott以降はともかく、比較的規模の大きなPentium 4でも、「Willamette」「Northwood」は3000万トランジスター弱で実現できている。

大雑把に言えば、2命令+αのP6コアで1500万トランジスター。3命令のPentium Mが2000万トランジスター。3命令+αのCore 2で3000万トランジスター強。4命令のCore i7で3500万~5000万トランジスター程度あれば、CPUコアを構成できることがわかる。最近では、CPUダイ全体のトランジスター数は10億個を超えている。つまり、CPUからGPUやPCI Expressなどを省き、共有2次/3次キャッシュなども省いてしまえば、20コアのCPUでもわりと簡単にできる計算になる。

もちろん、こんなCPUではメモリーアクセスが間に合わないから、コアの数をこんなに多くはできない。そこに共有2次/3次キャッシュを入れてもまだトランジスターはあまるわけで、GPUを統合するというのは、トランジスターの有効利用の観点から見ても適切な使い方だというのが考えられる。

ただ逆に言えば、長期的には広帯域なメモリーインターフェース技術である「WideIOのようなソリューションと組み合わせれば、飛躍的にコアの数を増やすことが可能にもなる。つまり、単純にGPUの統合や高機能化以外の可能性もあるのが、現状のインテルのアーキテクチャーである、という見方も可能だろう。

次回は、AMDのコアを同じように分析してみたい。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ