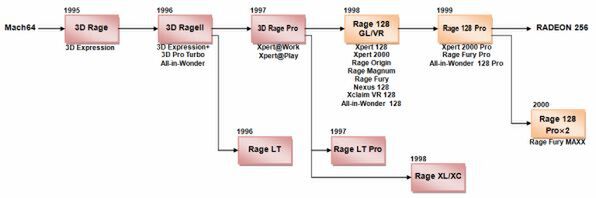

RADEON登場までのつなぎに

デュアルGPUのRage Fury MAXXを開発

長い前置きが終わったので、ようやく本題に入ろう。Rage 128 Proに続いてATIは、のちにRADEON 256として投入される「R100」コアの開発を進めるが、これが予想外に難航してしまう。ところが競合するNVIDIAは、いち早く「GeForce 256」を投入。また、S3がDirectX 7対応の「Savage 2000」を開発している話も早くから聞こえてきていた。これらに対抗するための“つなぎ”製品が、ATIには必要だった。

そこでRage 128 Proをカード1枚に2個搭載して、AFR(Alternative Frame Rendering)を使って描画性能を倍増させるという、よく言えば意欲的、悪く言えば無茶な製品が登場する。それが「Rage Fury MAXX」であった。

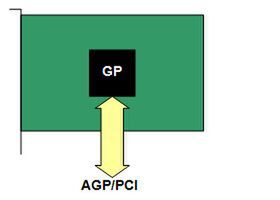

どの辺が無茶だったかと言うと、チップの接続方法が本来やってはいけない構造になっていたことだ。例えば図1のような構成の、ごく当たり前のグラフィックスカードがあるとする。GPU自身がAGPやPCIのインターフェースを内蔵しており、これを使ってマザーボードと接続するという仕組みだ。

図1 一般的なAGP/PCIインターフェース内蔵のグラフィックチップとグラフィックスカードの接続方法

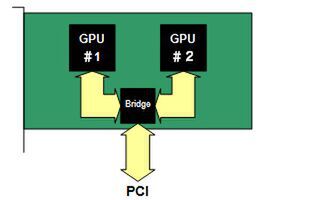

このGPUを2つ、1枚のカードに載せたいと思ったらどうするか? それは図2のように、ブリッジチップを介して2つのGPUを接続することが必須となる。これはPCIの仕様が、原則として1スロットにひとつのデバイスしか接続されないという前提で、初期化あるいはアクセスを行なうためだ。だが、その例外として「ブリッジチップが入った場合のみ」と規定されているので、こうした方式が必須となる。

図2 図1のグラフィックチップを1枚のカードに2つ載せる際の実装例

例えば、図2のケースでGPU #2に何かさせようという際に、チップセットから見るとGPU #1とGPU #2は同じスロットに刺さっているので、区別が付かない。そのうえGPU #1とGPU #2は同じI/O空間を共有することになるので、ブリッジチップを介さない構成でCPUからデータを書き込もうとした場合、同時に両方のGPUにデータを書き込むことになる。逆に、GPUから何かデータを返す場合も、両方が同じアドレスでデータを送り出すから区別できない。こうした問題を回避するために、間にブリッジチップを挟むわけだ。

ところで、図2にAGPと書いていないのは意図的なものだ。AGPはブリッジチップをサポートしていなかったからである。AGPはベースが66MHz/32bitのPCIバスなので、理論上はブリッジが使えるはずである。ところがAGPで拡張された「Side Band Addressing」や「GART」(Graphics Address Remapping Table)といった機能は、複数のGPUがブリッジ経由で接続されることを考慮していない。これらをサポートすると、プロトコルや機構が複雑になりコストが上がるからだ。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ