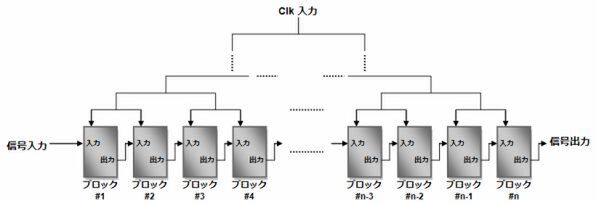

一番簡単なのは、クロックの配線を等長にすることだ。図2はこの方法によるクロック信号のツリー配線である。各々のツリーから分岐する長さが必ず等しくなるように工夫すると、(完全には難しいとしても)かなり位相のずれは抑えられる。ところが、これでは配線量が爆発的に増えてしまうため、これを全面的に使うというケースはさすがにほとんどない。

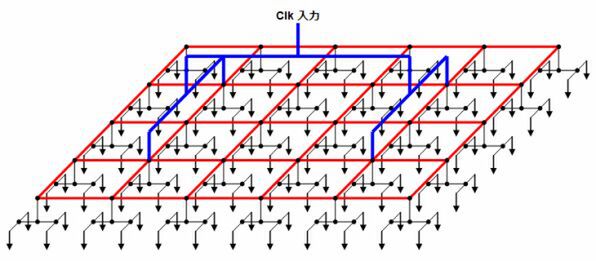

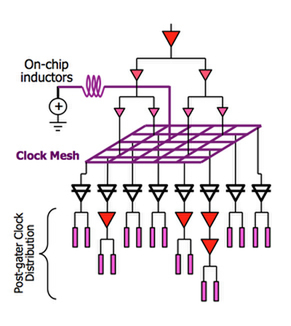

その代わりに多く利用されているのが、「クロックメッシュ」(図3)である。赤い配線がメッシュで、これを回路全体を覆うように配置して、そこの縦横の交点からさらにツリー構造などで信号を分配して、それぞれの回路ブロックに供給する。クロックメッシュ自身には、適当な場所(図3なら青い配線で供給される4ヵ所)に対してクロック信号を供給する。これにより、ずれを最小に抑えながら回路全体にクロック信号を供給することができる。

この方式の欠点は、クロック信号の駆動に結構な電力を消費することだ。なにしろ信号速度は今や4GHzだし、メッシュを構成する配線の抵抗や、それより大きいものとしてクロックメッシュの寄生容量※1も問題になってくる。図3には入れていないが、実際にはクロックメッシュの各交点から信号を引っ張り出したあとで、クロックバッファと呼ばれるクロック信号のブースターが間に挟まって実際の回路ブロックに供給される。このブースターの消費電力も馬鹿にならない。

※1 意図せずにコンデンサーとして作用するという意味。この場合、クロックメッシュの配線がコンデンサーとして作用することを意味する。

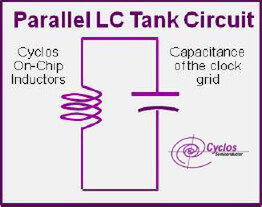

こうした消費電力を減らすための方法が、今回の共振クロックメッシュ(Resonant Clock Mesh)である。これの理屈は「LC回路」をベースにしたものだ。LC回路というのは下の画像のように、コイル(L)とコンデンサー(C)で構成されるもので、「f=1/(2π×√LC)」という周波数で発振することが知られている。

先ほど述べたように、コンデンサーの代わりはクロックメッシュの寄生容量が利用できる。あとはコイルの代わりとなるインダクターをどこかに設けてやれば、クロックメッシュ全体が発振することになり、元々のクロック信号を生成する電力が大幅に減らせる、という仕組みである。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ