Piledriverに導入される

「共振クロックメッシュ」とは?

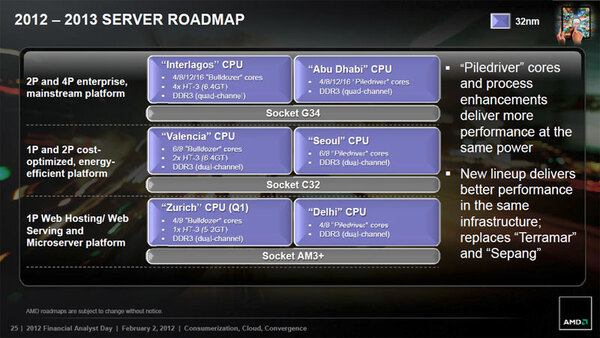

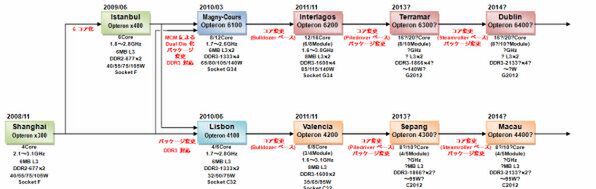

ロードマップの大枠の説明をしたところで、サーバー向けCPUとPiledriverコアについて、もう少し説明しよう。まずサーバー向けCPUから。上の画像は1ページめに掲載したサーバー向けCPUロードマップとほぼ同じスライドだが、右側の説明が異なっている。3ヵ月前の連載129回でのロードマップは下の図のとおりだったが、この時点では「Interlagos」の後継は「Terramar」、「Valencia」の後継は「Sepang」になっていた。

このTerramarが「Abu Dhabi」となり、Sepangが「Seoul」でそれぞれ置き換えられた。大きな違いは、以前の予定だとBulldozerの後継製品は10コア/5モジュールの製品の可能性が示唆されていたのが、今回はっきりと「ハイエンドでも8コア/4モジュールだ」と明示されたことである。やはり現在の32nm SOIプロセスでは、ダイサイズを大きくするのは困難だったようだ。

ロードマップ自身も若干の修正がある。Interlagos世代は12/16コア製品のみと129回でのロードマップには記載したが、実際には4/8コア製品も投入された。G34の場合、2つのダイをMCM(Multi Chip Module)で接続するのが原則である。つまり、2コア/1モジュールおよび4コア/2モジュールのBulldozerのダイを、MCMで接続したラインナップもあるということになり、これがPiledriverベースのAbu Dhabi世代でも継承されるようだ。

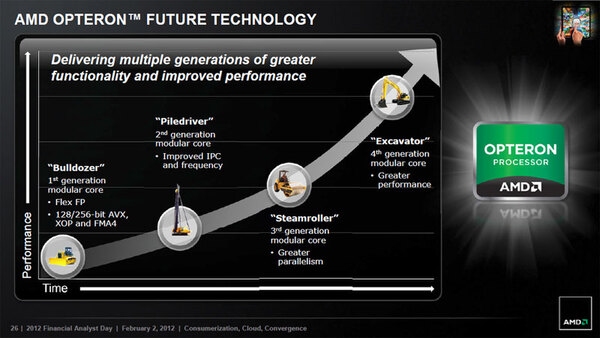

以前からPiledriverの世代では、IPCおよび動作周波数を向上させるという話があった。このうちIPCに関しては依然としてその詳細が不明であるが、動作周波数向上につながる工夫としてISSCCで発表されたのが、Cyclos Semiconductorの「共振クロックメッシュ」の技術を、Piledriverに実装したという話である。これをもう少し詳しく説明しよう。

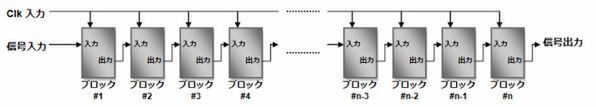

まず大前提であるが、CPUを初めとするほとんどのデジタル半導体は、同期回路と呼ばれるもので構成される。「何が」同期しているのかと言うと、内部の細かな回路ブロックが、全部同じタイミングで動作するという意味である。図1はn個の回路ブロックが直列でつながっているケースである。

この場合、すべての回路ブロックにクロック信号が供給され、このクロック信号の立ち上がり(倍速だと立ち上がりと立ち下がり)のタイミングで信号の取り込み、および信号の出力を行なう。クロック信号という“掛け声”にあわせてバケツリレーをすることで、効率よく処理を実行させようという仕組みだ。

理論上はこれでいいのだが、実際に実装する場合、クロックの“ずれ”が問題になる。ようするに「配線による遅延」だ。図1で言えば、クロック信号源に一番近い「ブロック#1」と一番遠い「ブロック#n」では、だいぶ距離がある。このまま放置すると、クロック信号の位相のずれが発生する。もちろんある程度はマージンはあるが、1~2MHzで動いている回路ならともかく、4GHzともなるとクロックの周期が250ps(0.25ns)だから、マージンといってもせいぜい10ps程度であろう。伝達遅延をなんとしてもこの範囲内に収めないといけない。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ