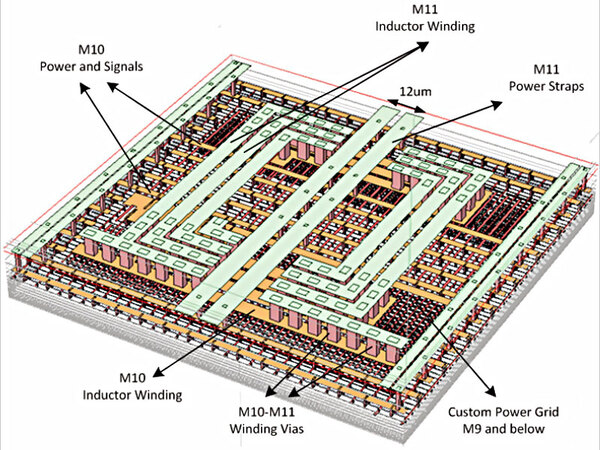

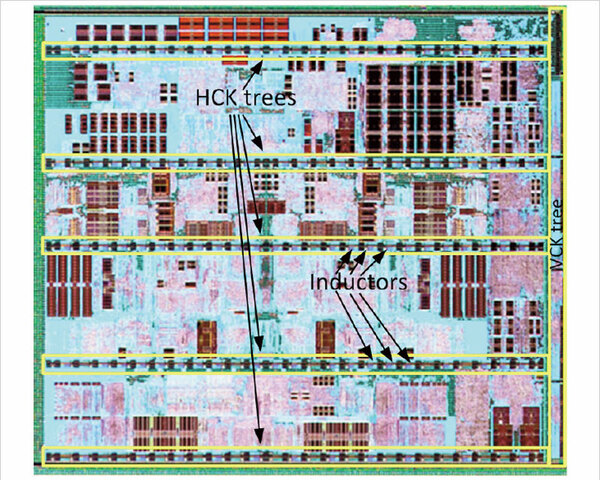

ISSCCでの発表によれば、1つのPiledriverコア上に、5本の「HCLK Tree」が構成され、1本あたり54の「Clock Driver」と25個のインダクターが装備されるという。下の画像は配線の様子で、第10層(M10)と11層(M11)の配線が、この共振クロックメッシュに利用されていることがわかる。

ここで問題になるのは、コイルに相当するインダクターをどう回路上に集積するかである。先のホワイトペーパーでは1GHzクラスのクロックの場合に必要なインダクタンスは0.75nH~1.25nH※2で、これはおおむね100×100μm2程度に収まるとのことだ。ISSCCの発表ではダイの写真も示されたが、確かにそれほど問題になる大きさには見えない。

※2 コイルの誘導係数の値。単位はH(ヘンリー)

肝心なのは、この方式を採用した効果であるが、クロック信号の供給に必要な電力を最大24%削減できて、3.2GHz~4.4GHzの範囲で問題なく動作すると発表されている。システム全体の消費電力では、共振クロックメッシュを使うことで同一周波数なら5~10%の消費電力削減となり、同一消費電力ならば動作周波数を100MHz引き上げることが可能、とされている。

ISSCCでの発表は共振クロックメッシュに関する話だけで、肝心のPiledriverの性能などは一切公開されていない。これについては、2012年夏の半導体関連イベント「HotChips」あたりの情報を待つしかなさそうだ。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ