MemoryLogix MLX1

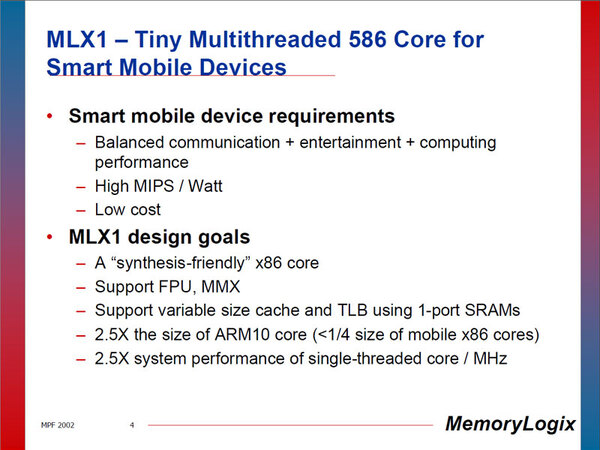

まったく異なるアプローチで、x86市場に参入を試みたベンダーもある。2000年に創業されたMemoryLogix社がそれだ。同社はモバイル分野、正確にはARM10/11が使われるような携帯機器にx86 CPUを使うことを想定。これに適したプロセッサーを開発し、IPライセンスとして提供するビジネスを始めようとした。

以下の画像は、MPF2002での同社講演資料からの引用である。例えばプロセスを同一と仮定した場合、ARM10のダイサイズを1とすると、既存のx86プロセッサーはどれもARM10の10倍以上のダイサイズを必要としている。同社はこれを、ARM10の2.5倍程度で実現しよう、という目標を掲げた。

| プロセッサー | ARM10基準のサイズ比 |

|---|---|

| ARM10 | 1 |

| インテル ULV Pentium III-M | 13 |

| AMD Duron | 14 |

| トランスメタ Crusoe TM5800 | 10 |

| VIA C3 | 12 |

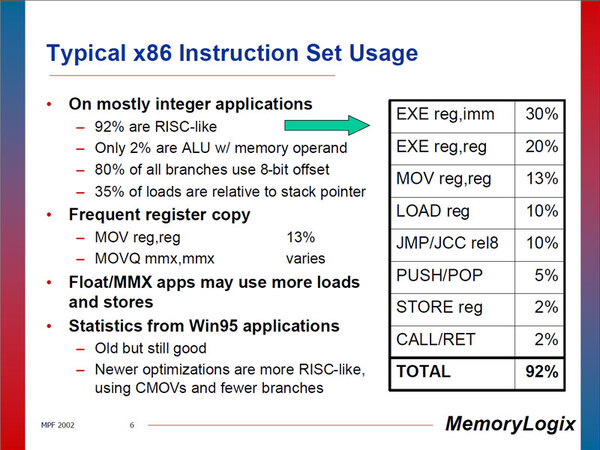

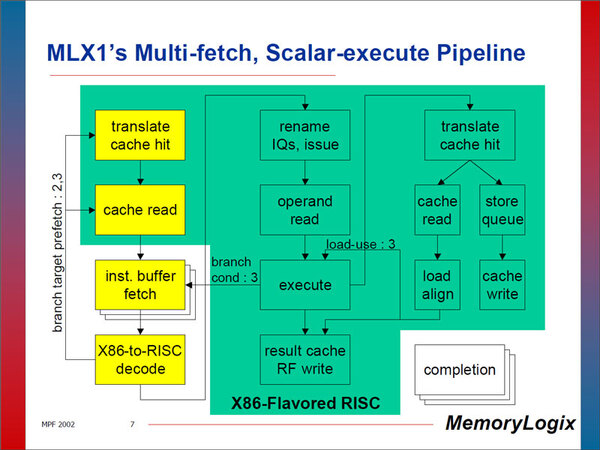

これをどう実現するのかだが、まずは稼動しているWindows 95上でのアプリケーションを調べる。ほとんどの命令はARMでも使われている典型的なRISC命令なので、これらが高速に実行できればそこそこに性能が出る。こうした目処を元に、それを実現するシンプルなCPUコアを設計したというわけだ。

ちなみに設計目標(シミュレーションの結果らしい)では、0.13μmプロセスで400MHz駆動を想定した場合、CPUコアが3.5mm2で、MMXユニットが1.0mm2、FPUが1.5mm2の合計6.0mm2で構成できるとしていた。ARMの「ARM 1026EJ-S」が同じ条件の場合、コアのみで2.6mm2、キャッシュ込みで4.6mm2程度になるので、おおむね2.5倍という目標がはたせたとしていた。

これが実現していれば、Atomなんぞを待たなくてもx86を搭載した携帯電話がありえたかもしれないが、あいにくそうはならなかった。最初に述べたとおり、MLX1はIPライセンスでの提供なので、どこかの半導体ベンダーがこのIPを買って、SoCの形でシステムを作る必要がある。だが、そうしたベンダーはついに出現せず、MemoryLogix自身が破綻してしまう。

その後、(一時期トランスメタのCEOを務めたこともある)Matt Perry氏が立ち上げたMontalvo Systems社に、MemoryLogix創業者のPeter Song氏も参画。さらにx86のシミュレーターや仮想化に詳しいKevin Lawton氏も加わって、今度はファンドなどから大量に資金を集めて、やはりMLX1と似たようなプロセッサーの開発を始めた。しかし、こちらも製品が出る前に破綻しかかり、最終的にSun Microsystemsに買収されて終わった。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ