マルチプロセッサー対応では、最大63個のプロセッサーを同時に駆動することが可能となっていた。複雑なのは、単一のプロセッサーが複数並ぶという構成以外にも、巨大な実行ユニットを持つ単一プロセッサーといった構成も可能な点だ。ソフトが対応すればこうした利用法も可能だった。

マルチタスクとは、複数のプログラムを同時に実行できる仕組みである。またこの複数のプログラム間で連携、あるいは通信を行なうための手段として、プロセス間通信機能をCPU内部で実装している。こうした機能は通常OSで実装されるのが常で、CPUはこれを実現するための基本的な機能のみを提供するケースがほとんどであった。

これらよりも、もっとiAPX 432を特徴付けているのがオブジェクト指向である。ここで言うオブジェクト指向とは、複数のデータ型を取り扱える「オブジェクト」という考え方を、内部のデータ管理の基本に置いたことである。これを実現するため、例えばデータやプログラムではメモリーアドレスをそのまま扱えなかった。メモリーアドレスは「セグメント+オフセット」の形で示される。

このセグメントとオフセットという名前は、後の「Intel 8086」でも出てくるものだが、同じなのは名前だけで使い方はだいぶ異なる。iAPX 432の場合、このセグメント+オフセットをまとめて「AD」(Address Descriptor)と呼ばれるデータ構造で扱っており、プログラムはこのADを使って記述する必要があった。またオブジェクトを生成するための方法も、「CBA」(Capability Based Addressing)と呼ばれる独特な方法を採用した。

最後の入出力であるが、iAPX 432では「IP」(Interface Processor)と呼ばれるチップを使うことで、従来型のCPU(例えば8080)をシステムに接続することが可能であった。

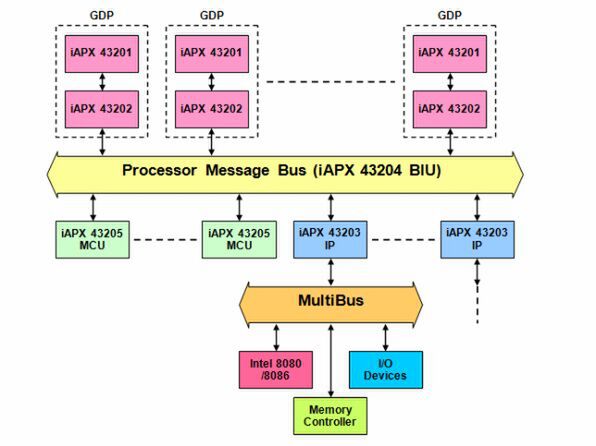

iAPX 432システムの構成

iAPX 432のシステムは上図のような構成となる。各々のプロセッサーコアは「GDP」(General Data Processor)と呼ばれて、「iAPX 43201」と「iAPX 43202」の2つのチップから構成される。他にメモリーコントローラーが「iAPX 43205 MCU」(Memory Control Unit)、入出力が「iAPX 43203 IP」(Interface Processor)となっている。

先ほど「最大63プロセッサー」と書いたが、このプロセッサーとは「GDPとIPをあわせて最大63個」となる。GDPやIP、MCUは専用の「Processor Message Bus」で相互に接続されるが、このバスは実際には「クロスバースイッチ」と呼ばれる高速な接続方法で構成された。このクロスバースイッチを構成するのが「iAPX 43204 BIU」(Bus Interface Unit)である。

iAPX 432システムの場合、外部とのI/OはすべてIPを経由する必要があった。このIPの先には、インテルが8080時代に標準化した「MultiBus」という汎用バスが接続されている。そしてMultiBus上に、8080ないし8086と、これら用のメモリーコントローラー、そしてI/Oデバイスがぶら下がるという非常に複雑な構成になっていた。もっとも、BIUとMCUはGDP/IPからやや遅れて出荷されることになっていたので、当初はシングルプロセッサー構成しか作れなかった。

巨大で複雑すぎたiAPX 432

製造は困難で性能も低く……

iAPX 432は意欲的な構成であったが、問題は山積みであった。まずGDPだが、これが2チップ構成になったのはあまりに構造が複雑すぎて、当時の半導体製造技術では1チップ化できなかったからだ。そのために内部を二分割して、命令デコードまでを行なうiAPX 43201と、それを実行するiAPX 43202に分けて実装した。だがそれでもiAPX 43201が66.3mm2、iAPX 43202は74.0mm2という(当時としては)巨大なダイサイズに肥大化してしまった。ちなみにiAPX 43203 IPはさらに巨大で、75.3mm2ものダイとなっている。

一方で、Intel 8080は20mm2、Intel 8086で33mm2、最終的にiAPX 432に取って代わることになった「Intel 80286」でも47mm2でしかない。厳密に言えば、それぞれプロセスが微妙に違うから単純にダイサイズで比較するのは公平ではない。だが当時の製造技術からすれば、ダイサイズが大きくなるとそれだけ歩留まりが激しく悪化した。直径300mmが当たり前の今と異なり、ウェハーサイズそのものが2インチ(直径50mm)~4インチ(直径100mm)の時代だから、ダイサイズが大きいチップは非常に製造が困難だった。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ