次世代の本命「WideIO」は遅れ気味

GPU向けの展開はあり得るか?

LPDDR2に続いて、現在標準化作業の最中なのが「LPDDR3」と「WideIO」である。LPDDR3はLPDDR2の延長ながら、最大で6.4Gbpsまでの転送を可能にしたものだ。LPDDR3が検討されている理由は、後述するWideIOが「予想以上に」と言うか「予想通りに」と言うべきか、実現が遅れていて、中継ぎが必要と判断されたからである。

LPDDR3は既存の技術の延長線上で実現できるから、WideIOが広く利用されるようになるまでの間に、急激に高まっている広帯域メモリーのニーズへの対処として、とりあえず投入したいというのがJEDECの意向である。

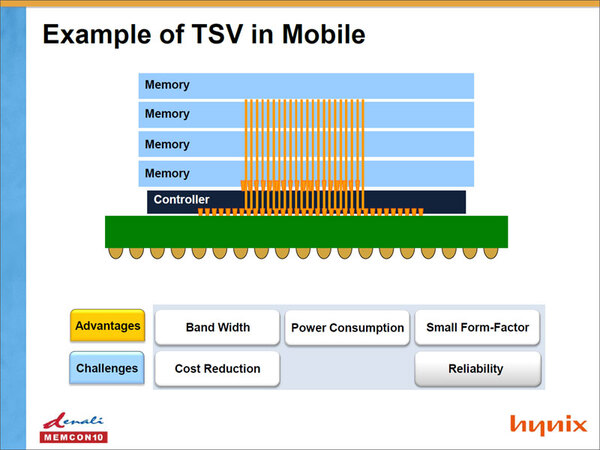

そして最後に登場するのがWideIOである。かつては「3D-RAM」などとも呼ばれていたが、端的に言えば「TSV」(Through-Silicon Via:シリコン貫通ビア)を使ってメモリーを広帯域で接続しよう、というものである。

従来のSDRAM系では、メモリーチップのピン数をそれほど増やせないから、DDRのように信号速度を上げることで、必要なメモリー帯域を確保しようとした。しかし信号速度向上にともなって、消費電力が増えてしまう問題がある。そこで、「ピンの数を大幅に増やしつつ信号速度を抑えることで、消費電力も低減しよう」というのが、WideIOの基本的な考え方である。

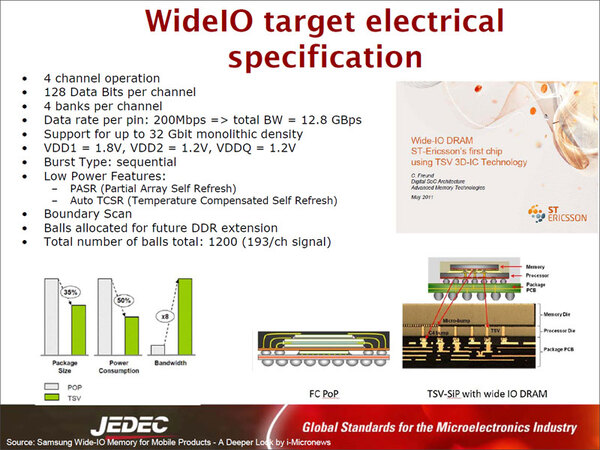

まだ標準化までには時間が掛かるが、とりあえず最初に想定されているのは、128bit/チャンネルの帯域だ。これが4チャンネル(計512bit)のバス幅を持つ一方で、信号速度は200Mbpsに抑えることで、トータルでは12.8GB/秒の帯域を確保する計算になる。チップの容量も32Gbit品あたりまでは考慮している。これ以上が必要な場合は、上掲のスライドのように複数を積み重ねることになるだろう。

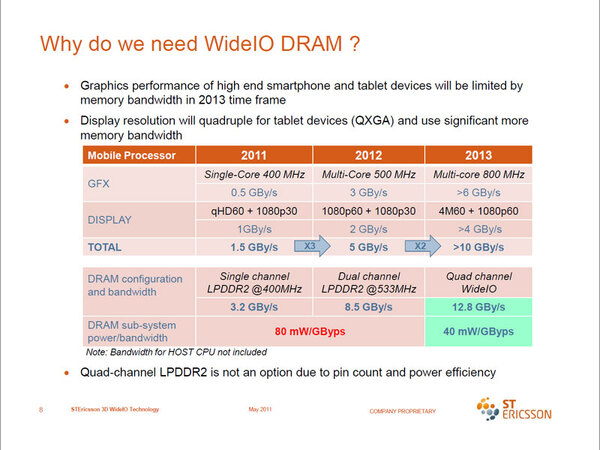

WideIOの標準化のスケジュールだが、2011年6月いっぱいでドラフト案の変更を終了し、9月に標準化したものをリリースしたいという話であった。メーカーの中にはもう少し楽天的なところもあり、たとえばST Ericsson社のC.Freund氏の資料では、2013年にはWideIOを実装した携帯電話用SoCをリリースできるとしている。携帯機器でもグラフィックス周りのメモリー帯域不足は如何ともしがたいようで、まずはここにWide IOを投入したいようだ。

ただしWideIOは、今のところモバイル用途のみを想定するという話である。問題なのは熱だ。TSVの説明スライドからもわかるとおり、WideIOはコントローラー上に直接メモリーチップが搭載される。この構造では、巨大なヒートシンクと冷却ファンが必要なPC向けCPUや、TDPが200Wを超える昨今のGPUに使うと、間違いなくメモリーチップが先に逝ってしまうだろう。

またこうした高温環境では、熱による素材の変形やこれにともなうTSVの接続不良、材料の変質なども、かなりシビアな問題になってくるだろう。とにかく低消費電力が要求されるモバイル向けだからこそ、比較的早期に可能になったという話で、汎用プロセッサーとかGPUにこれが利用できる日はまだ遠いようだ。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ