PS3への採用で世に出たXDR DRAM

PC用にXDIMMも開発

ちなみにXDR DRAMは、クロック信号の8倍速(ODR、Octal Data Rate)で駆動される。初期のXDR DRAMは400MHzクロックで3.2Gbpsのデータレート。XDR DRAMチップのバス幅は16bitとなっており、XDR DRAMチップ1個で6.4GB/秒の帯域になる。

XDR DRAMを最初に採用したのは、ご存じ「プレイステーション3」(PS3)だ。初期ロットのPS3はこれを4つ利用して, 合計25.6GB/秒の帯域を確保した。

XDR DRAMの開発当初は、まだPC用メモリーへの未練が若干あったようで、「XDIMM」というDIMMモジュールも開発されている。これはXDR DRAMをDIMMに装着して利用できるもので、物理的にはDirect RDRAM用のRIMMと共通のコネクターに装着できるようになっていた。XDIMMのバス幅は32bitで、1枚あたり12.8GB/秒(3.2Gbpsの場合)~25.6GB/秒(6.4Gbpsの場合)の帯域となる。

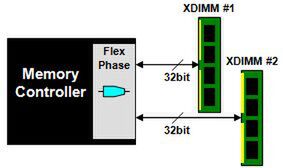

ただし、XDR DRAMはディファレンシャル方式であるがゆえに、メモリーコントローラーとの接続はポイント・ツー・ポイントに限られる。そのため、複数枚のXDIMMをひとつのチャンネルに装着できない。そこで2枚のXDIMMを装着する場合、図5の仕組みが考えられた。ようするに、「デュアルチャンネルXDIMM」というわけだ。これ以外にも、「ダイナミック・ポイント・ツー・ポイント」という仕組みも可能という。

図5 XDIMMとメモリーコントローラーの接続例 デュアルチャンネル

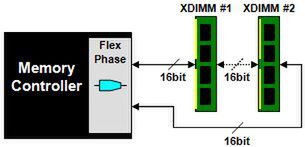

先に「FlexPhaseは配線などのズレを調整する」と説明したが、それ以外にバス幅の調整も可能である。図6は、2枚のXDIMMをそれぞれ16bit幅で接続しているケースである。この場合、FlexPhaseは各XDIMMのチップに対して、有効バス幅を半分にするように通知して、半分のバス幅で通信する。

図6 XDIMMとメモリーコントローラーの接続例 半分のバス幅での接続

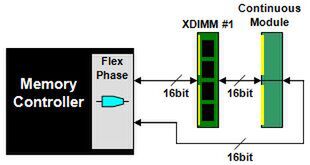

この接続を採用した状態で、XDIMMが1枚の場合はどうなるか? その場合、図7のように「Continuous Module」を装着して、これを経由することでメモリーコントローラーとXDIMMを32bitで接続する。Direct RDRAMにおけるC-RIMMのような仕組みだ。

図7 XDIMMとメモリーコントローラーの接続例 XDIMMが1枚の場合

この構成は、XDIMMの枚数によらず一定の帯域を利用できる利点がある。そのため商品構成上は有利になるという話だったが、残念ながらDirect RDRAMで十分懲りたPCベンダーはこの提案には載らなかった。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ