分岐を排除することが高速化への道

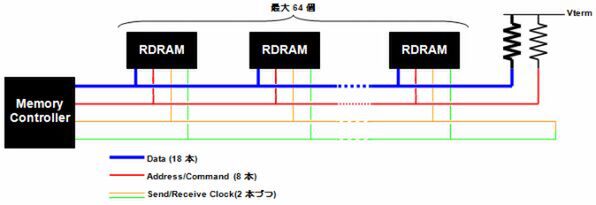

図1はDirect RDRAMの基本的な構造である。Base RDRAMやConcurrent RDRAMでは、配線数を削減する目的でDataとAddress/Commandを時分割多重化するという凝った構造になっていた。Direct RDRAMでは転送効率を引き上げるために、DataとAddress/Commandを分割したので、若干配線数は増えている。

Direct RDRAMでは1チャンネルの信号線に、最大64個までのメモリーチップをぶら下げられる。DataとAddress/Commandは終端抵抗を入れて反射波を削減しており、これはのちにDDRメモリーも同様の方法を採用している。一方で、送受信に利用するクロック信号は終端で折り返しており、これにより行き/戻りのスキュー(信号のズレ)を削減する仕組みだ。

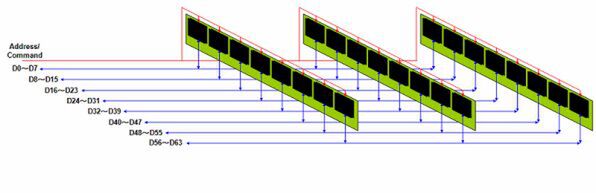

「基本的にはSDRAMと変わらないのに、どうして高速伝送が可能なのか?」と考える人もいるだろう。Rambusによれば、キーとなるのは「分岐を作らない」ことだという。連載98回で使った図を例に説明しよう。

この図を見ると、DIMMを介することでDataでは3ヵ所の分岐が、Address/Commandでは27ヵ所もの分岐が生じている。こうした分岐が信号を乱す最大の要因となるならば、分岐を排除すれば信号を高速化しても波形の乱れは生じない、となるわけだ。

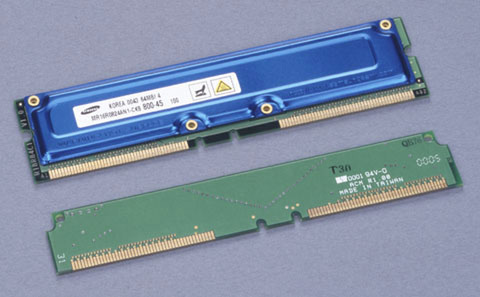

なお、図1でも分岐が生じているように見えるかもしれないが、実際の配線は一筆書きで終端抵抗までつながっている。この配線の真上に直接メモリーチップを接続することで、物理的な分岐の長さを最小限に抑えるように工夫している。Base RDRAMやConcurrent RDRAMのメモリーチップでは、まだリード(配線用の足)付きの「SOP」というパッケージだったが、Direct RDRAMでは「BGA」(Ball Grid Array)を使うことで余分なリード線を削減。分岐の最小化に努めた。

PC用メモリーモジュールとするために

「RIMM」と「C-RIMM」を開発

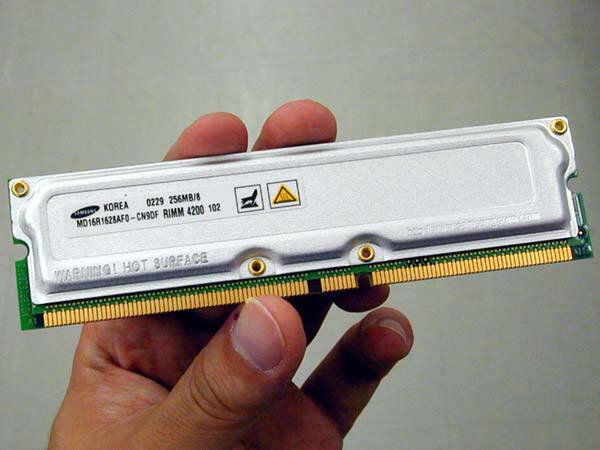

家庭用ゲーム機やグラフィックスカードのように、基板上にDRAMチップを実装する製品ならこれは簡単だ。しかし、PCではDIMMなどのメモリーモジュールを使い、ユーザーのアップグレードを可能とするシステムでなければ使えない。そこで考えられたのが「RIMM」(Rambus Inline Memory Module)である。

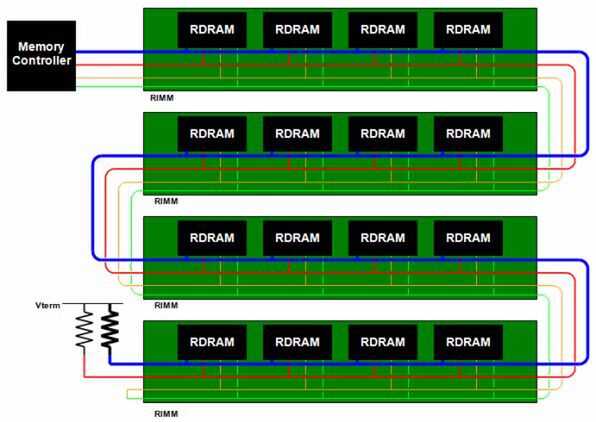

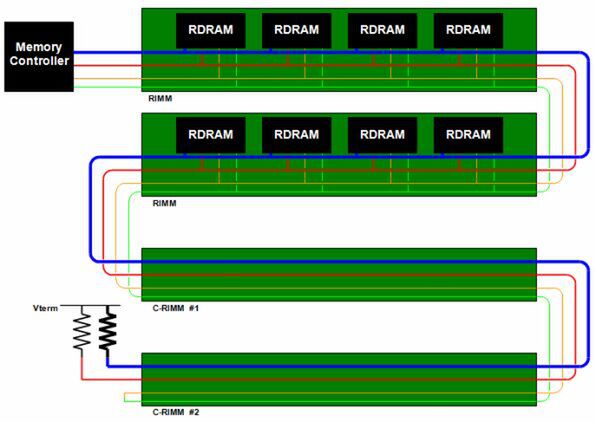

図2はRIMMを4枚装着する構造の説明図である。4枚のRIMMの配線が、一筆書きを構成するようになっているのがわかる。こうした構造とすることで、図1の構造を維持しながら、メモリーモジュールによるアップグレードを可能としたわけだ。

ただしこの構成では、SDRAMと異なり「空きスロット」が許されない。一筆書きが途切れてしまうからだ。これを避けるために「C-RIMM」と呼ばれるものが用意された。図3は2枚のRIMMと2枚のC-RIMMを使った例である。ようするに、C-RIMMは単に配線をつなげるだけの板で、RIMMを刺さないスロットにこのC-RIMMを装着しておけば、終端抵抗まで配線が全部つながるという仕組みだ。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ