LLCとリングバス

Nehalem世代とSandy Bridgeアーキテクチャーの大きな違いが、LLCとリングバスだ。今回からインテルは、「3次キャッシュ」を「Last Level Cache」という名称に変更した。これはおそらく、CPUとGPUでキャッシュを共有する構造になったためであろう。LLCはCPUから見ると3次キャッシュでも、GPUから見れば2次キャッシュになる(GPUは内部命令キャッシュを持つが、2次キャッシュは持たない)。そのため誤解を招かないように、LLCという名称にしたと思われる。

ちなみに、これに併せてCPUの2次キャッシュは「MLC」(Middle Level Cache)と称するようになったが、1次キャッシュは引き続き1次キャッシュのままである。

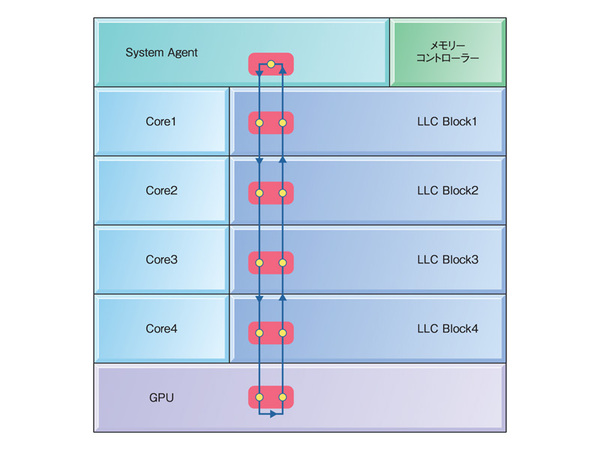

Nehalemの世代までは、3次キャッシュは大きなひとつのブロックになっていた。しかしSandy BridgeのLLCでは、これが複数個に分割されている。基本的には、CPUのコアと同じだけの数のLLCが、並列で用意されるという図8のような仕組みである。

これは「大量のデータを一気に格納する」という観点からすると、むしろ不利ではある。だが逆に、この複数のLLCは同時にアクセスが可能なので、トータルとしてのメモリー帯域は従来よりも大幅に上がっている。また、LLCの1ブロックあたりのサイズが小さくなっている分だけタグRAMの検索が高速になるため、レイテンシー短縮にも効果的である(関連記事)。

こうした複数のLLCをリングバスでつなぐ構造は、インテルのx86 CPUでは初めてというわけではない。最初に実装されたのはXeon MP向けのNehalem-EX(Xeon 7500番台)で、Sandy Bridgeのリングバスはこれのサブセットと考えていい。いきなり登場したわけではなく、インテルとしてはすでに実績あるシステムを改良してPC向けに投入したのだ。

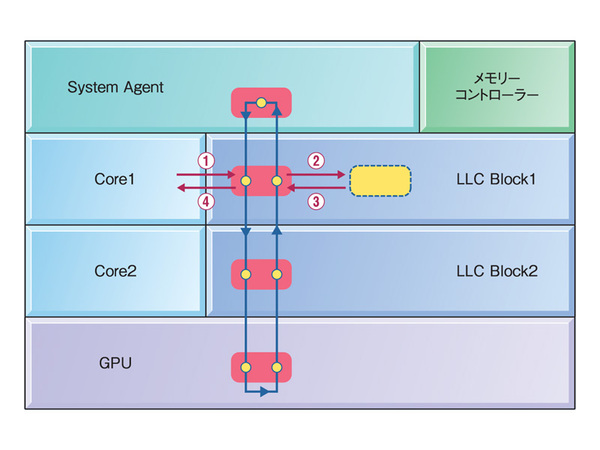

リングバスとLLCの動き方について、簡略化のためにCPUコアが2つの場合で解説しよう(図9)。まずCPUコア1がLLC Block1にあるデータをアクセスしようとした場合、以下の4ステップで動作する。

- ①CPUコア1はリングバス I/Fにリクエストを出す。

- ②リングバス I/FはLLC Block 1にそのデータがあると判断。リクエストをLLC Block 1に送る。

- ③LLC Block 1はリクエストされたデータを、リングバス I/Fに送り返す。

- ④リングバス I/Fはその結果をCPUコア1に転送する。

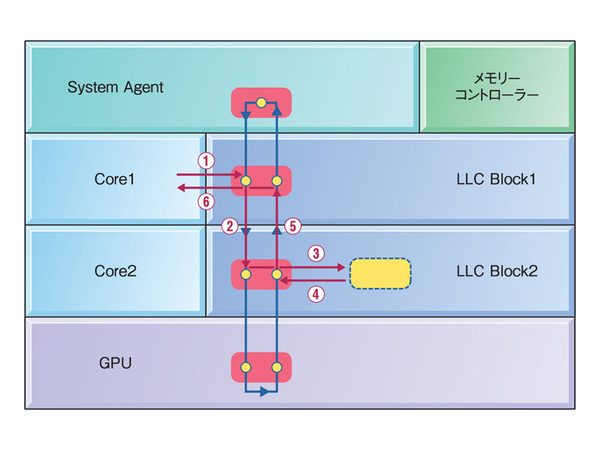

各々のステップは1サイクルで実行できるので、都合4サイクルで動作が完了するというわけだ。では最寄のLLCにデータがなかった場合は? それが図10である。

- ①CPUコア1はリングバス I/Fにリクエストを出す。

- ②LLC Block 1のリングバス I/Fは自身にそのデータはないと判断。リクエストをほかのBlockに送り出す。

- ③リクエストを受け取ったLLC Block 2のリングバス I/Fは自分が持っていると判断。リクエストをLLC Block 2に送り出す。

- ④LLC Block 2はリクエストされたデータを、LLC Block 2のリングバス I/Fに送り返す。

- ⑤LLC Block 2のリングバス I/Fは、その結果をLLC Block 1のリングバス I/Fに転送する。

- ⑥LLC Block 1のリングバス I/Fは転送されてきたデータをCPUコア1に送り出す。

この場合でも6サイクルで転送が完了する。この方式により、CPUコアからLLCをアクセスする場合の平均レイテンシは、2コアの場合で5サイクル、4コアの場合でも6.5サイクルと低く抑えつつ、同時アクセスできる帯域を2倍ないし4倍に増やすことに成功した。

ちなみにこの数字は、「2次キャッシュミス/3次キャッシュヒット」時の3次アクセスのみの話なので、CPUから見ると、もう少しレイテンシーは増える。1次/2次キャッシュミスであることを確認してからLLCにアクセスするため、実際にはこの数字に1次/2次キャッシュミスを判断するための時間が上乗せされる。

図ではひとつにまとめているが、このリングバスには「Data/Request/Acknowledge/Snoop」という4種類のバスがそれぞれ用意されている。図10の手順をより細かく書くとこうなる。

- ①CPUコア1はリングバス I/Fにリクエストを出す。

- ②LLC Block 1のリングバス I/Fは自身にそのデータはないと判断。リクエストをRequest Bus経由でほかのBlockに送り出す。

- ③リクエストを受け取ったLLC Block 2のリングバス I/Fは自分が持っていると判断。リクエストをLLC Block 2に送り出す。

- ④LLC Block 2はリクエストされたデータを、LLC Block 2のリングバス I/Fに送り返す。

- ⑤LLC Block 2のリングバス I/Fはその結果を、Data Bus経由でLLC Block 1のリングバス I/Fに転送する。同時にそのことをAcknowledge Bus経由で通知する。

- ⑥LLC Block 1のリングバス I/Fは転送されてきたデータをCPUコア1に送り出す。

それぞれのバスは独立して動作するので、ほかのコアによる転送を同時に行なうことも可能である。特にCPUの全コアがフルに動作しているときでも、支障がないように配慮されているわけだ。

この連載の記事

-

第13回

PCパーツ

マザーないけど…… Sandy Bridgeの「Core i3」がデビュー! -

第12回

PCパーツ

不具合によりP67/H67搭載マザーが全ショップで販売停止中 -

第11回

マザーボード

インテル、Intel 6チップセットのエラーを公表 -

第10回

PCパーツ

Sandy Bridge発売日にインテルがイベントを開催 -

第9回

マザーボード

「Sandy Bridge」対応マザーボード一斉発売!【その他編】 -

第8回

マザーボード

「Sandy Bridge」対応マザーボード一斉発売!【Intel編】 -

第7回

マザーボード

「Sandy Bridge」対応マザーボード一斉発売!【Gigabyte編】 -

第6回

デジタル

「Sandy Bridge」対応マザーボード一斉発売!【ASRock編】 -

第5回

マザーボード

「Sandy Bridge」対応マザーボード一斉発売!【ASUSTeK編】 -

第4回

PCパーツ

自作ユーザー集結! インテル新CPUが深夜に販売解禁! -

第3回

自作PC

ついに登場! 新型Core i7/i5シリーズの価格をチェック - この連載の一覧へ