ARM11のパイプライン構造

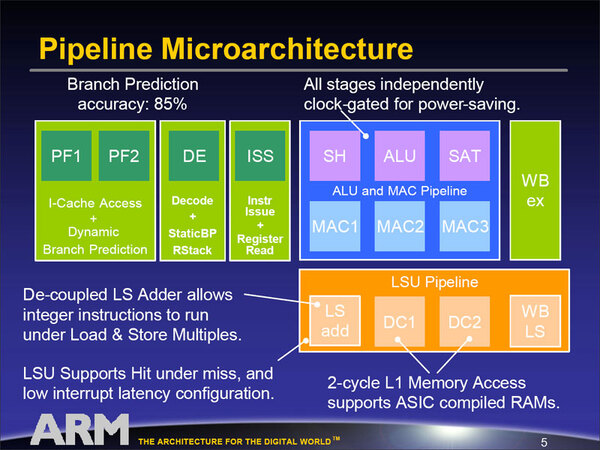

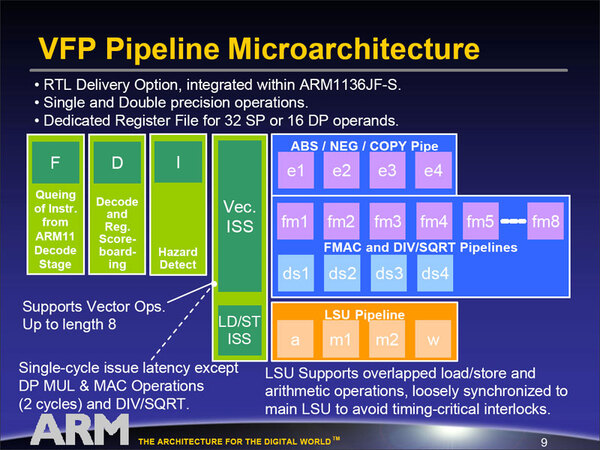

続いて内部構造について説明しよう。図2が整数演算パイプラインで、図3が浮動小数点演算のパイプライン構造となる。誤解を招かないように書いておくと、ARM11は基本的にシングルイシュー/インオーダーのプロセッサーである。図2ではまるで2命令同時実行が可能なように見えるが、もちろんそんなわけはない。単に実行ユニット部が「ALU/MACパイプライン」と「LSUパイプライン」に分かれている、というだけの話である。これは図3のVFPも同じである。

ちなみに、なぜ「VFP」と言うかといえば、ARM v5まではSIMDはサポートされていなかったため(XScaleの独自拡張であるWireless MMXは除外する)、ARM10までは「FPU」と称していた。ところがARM v6でSIMD拡張が行なわれ、FPUがSIMD演算をサポートしたために、VFPと称するようになったわけだ。

ARM11のパイプラインは、整数演算が8段、浮動小数点が8~16段という、組み込みプロセッサーとしてはやや長いパイプライン構造となっている。もっとも2002年といえば、インテルは「Northwood」(Pentium 4)、AMDは「Palomino」(Athlon)をリリースしていた頃だ。前者は20段、後者ですら10段のパイプラインだから、これに比べればまだ少ないという言い方もできる。

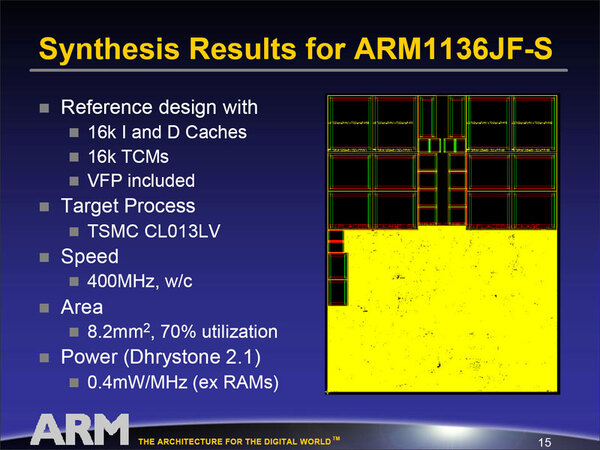

このARM11の発表の際には、リファレンスデザインの実装例も示された(図4)。TSMCの130nm LVプロセスを使い、最悪でも400MHzで動作すること、その際の消費電力は(外部のメモリーを除くと)0.4mW/MHz、つまり400MHz駆動で160mWにすぎないこと、エリア面積(ダイサイズとは異なる)は8.2mm2程度で収まることなどが紹介された。

このARM1136J(F)-Sが、ARM11初のコアである。これに続き、「Thumb-2」という新しい拡張命令搭載した「ARM1156T2(F)-S」が2003年10月に発表された。翌2004年にはさらに、「TrustZone」というメモリー保護機構を搭載した「ARM1176J(F)-S」がリリースされる。

ARM1136J(F)-Sは公称1.25DMIPS/MHzの性能を備えており、この数字はARM1176J(F)-Sも変わらなかったが、Thumb-2を搭載したARM1156T2(F)-Sは、1.41DMIPS/MHzに達している。その一方で、製造プロセスの改善による性能向上の効果も著しい。ARM1156T2(F)-Sは台湾TSMCの「90nm G(標準)プロセス」で600MHz駆動、消費電力は0.42mW/MHz、エリア面積は1.75mm2となっている。

もっと上を行くのがARM1176J(F)-Sで、TSMCの40nm Gプロセスを使うことで990MHz駆動が可能になり、エリア面積は1.17mm2、消費電力は0.105mW/MHzまで押さえ込めるとしている。TSMCの40nm Gプロセスはごく最近のプロセスだが、当時のTSMCの90nm Gプロセスを使っても、252mWほどの消費電力で840DMIPS程度の性能だから、これは十分に高性能と言える数字である。

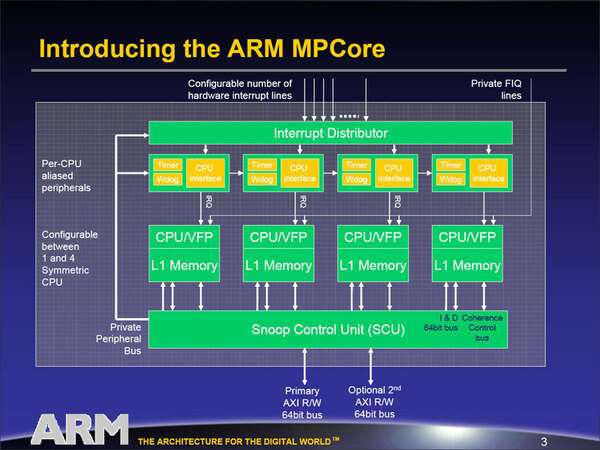

これらの改良で性能不足に対応したほか、さらにARMはARM v6をベースにしたマルチプロセッサー構成のアーキテクチャーを、2004年5月に開催された組み込み機器向けイベント「EPF(Embedded Processor Forum) 2004」で発表した。これは「ARM MPCore」として製品化されている(図5)。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ