論文概要に見えるBulldozerの姿

というわけで、前ページの写真はさっぱり参考にならないが、ISSCCの講演概要では、もう少しちゃんとした細かい情報が出ている。こちらは論文で出すものだから、まず間違いないと考えていいだろう。AMDはISSCCのセッション4(Enterprise Processors & Components)で2つの論文を発表することが、概要から見て取れる(AMDはほかにも論文を発表するが、直接Bulldozerに関係しそうなのはこの2つ)。

- 4.5 Design Solutions for the Bulldozer 32nm SOI 2-Core Processor

- 4.6 40-Entry Unified Out-Of-Order Scheduler and Integer Execution Unit for the AMD Bulldozer x86-64 Core

論文の概要には以下のようにある。

- CPUモジュール(つまり2つの整数コア+FPU)は2.13億トランジスター。32nm HKMGプロセス(High-K Metal Gate、高誘電率メタルゲート)で製造され、配線層は11層。

- 動作電圧は0.8V~1.3V。

- マイクロアーキテクチャーは従来のAMDの64bitプロセッサーよりも改善。その一方でダイサイズと消費電力を節約している。

- 従来に比べてゲート/サイクル数を節約しており(つまりより少ないトランジスタで高速動作が可能)、3.5GHz以上で駆動可能。また2MBの2次キャッシュを含んだCPUモジュールのダイサイズは、30.9mm2となっている。

- 整数演算ユニットのスケジューラーは、40命令をOn the fly(直接)で扱え、同時に4つの演算ユニットに命令を供給できる。

- (恐らくスリープ状態から)1サイクルで(稼動状態に)復帰する。

- 整数演算ユニット同士で、1サイクルでの命令バイパスが可能。

- クリティカルパスは標準的な設計技法で製造されており、独特なテクニックあるいはフルカスタムデザインに大きく依存した作りにはなっていない。

- 設計全体は消費電力を最小するように最適化した。

恐らく、2月にはこれらについてもう少し詳細な説明があると思われる。「命令バイパス」だけがちょっとピンと来ないのだが、2月の説明を待ちたいところだ。

前半の話はいいのだが、面白いのは最後から2番目だ。原文では以下のように書かれている。

「Critical paths are implemented without exotic circuit techniques or heavy reliance on full-custom design」

この書き方からすると、流石にスタンダードセル(カスタム設計)そのままというわけにはいかなかったが、クリティカルパス(遅延の大きい経路)だけを「Low Vt」なトランジスター※1を使った、という程度に考えておけばいいのかもしれない。

※1 高速だがリーク電流が多い、しきい値電圧の低いトランジスター。

2013年には「次世代Bulldozer」が登場?

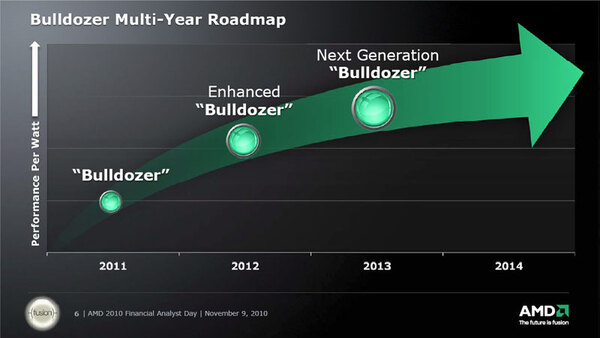

プレゼンテーションに戻すと、今回明らかになったのは、2012年にはBulldozerの改良型、2013年には「次世代Bulldozer」が登場することだ。ただ、ここでの改良はあくまでも「Performance per Watt」(消費電力当たりの性能)の改善にあるとしており、プロセスの微細化もここには含まれると思われる。そのため、マイクロアーキテクチャーの変更がどの程度予定されているのかは、今のところ未知数である。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ