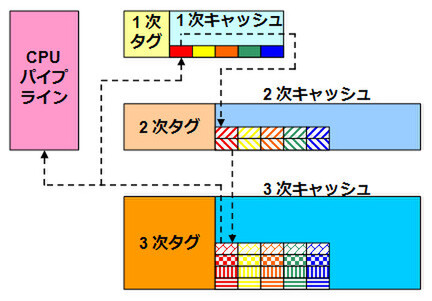

ではこれがExclusive Cacheだとどうなるか? 前ページと同様に1次ミス/2次ミス/3次ヒットのケースでの読み込みから見てみよう(図7)。

- ① 1次タグを検索→1次キャッシュミス

- ② 2次タグを検索→2次キャッシュミス

- ③ 3次タグを検索→3次キャッシュヒット

- ④ 3次キャッシュからデータをフェッチしてCPUパイプラインに取り込み

- ⑤ 1次キャッシュからリフィル対象となる1ライン分をいったん別の場所に保持

- ⑥ フェッチしたデータを、⑤で空けたラインにフィル

- ⑦ 2次キャッシュからリフィル対象となる1ライン分をいったん別の場所に保持

- ⑧ ⑤で保持したデータを、⑦で空けた場所にフィル

- ⑨ ⑦で退避したデータを、④により空いたラインに格納

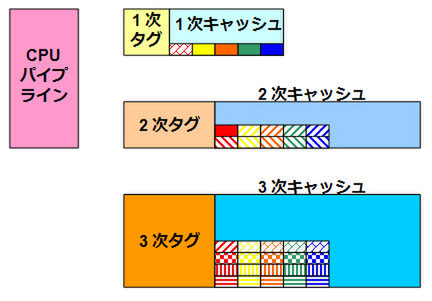

最終的には図8のように、キャッシュ内のデータの持ち方が入れ替わるのがExclusive Cacheの動作となる。

言うまでもなく、これは結構手間のかかる作業である。①~④まではInclusive Cacheと同じ動作だが、⑤~⑨がまったく異なるわけだ。もちろん、理論上は⑤~⑨までの処理は④の後で行なえるのだが(見かけ上CPUパイプラインのレイテンシー増にならない)、この処理は毎サイクルごとに発生する。例えば、前のサイクルでいったん2次キャッシュに退避させたはずのデータを、次サイクルでフェッチしようとしたなんて場合を考えると、前のサイクルの⑧が完了するまで、次サイクルの2次タグ検索はできない。

ようするに、形は違うがCPUにパイプラインストール(関連記事)が発生していることになり、あまりここで時間をかけるのはよろしくない。その結果、ある程度時間が掛かっても⑤~⑨はまとめて実行したほうが安全になるので、結果としてキャッシュアクセス時のレイテンシー増加につながることになる。Inclusive Cacheはこうした可能性がないから、レイテンシーはずっと短くなる。

AMDがExclusive Cacheを選択する理由とは?

ではなぜAMDは、こうしたレイテンシー増加(=性能低下)のペナルティを負ってまでExclusive Cacheを実装したのか? それはキャッシュの利用効率向上が図れるからだ。同じ4コア世代のAMD Phenom IIとインテル Core i7のデータ/ユニファイドキャッシュの容量を比較してみる。

| Phenom II | Core i7 | |

|---|---|---|

| 1次キャッシュ | 64KB/コア | 32KB/コア |

| 2次キャッシュ | 512KB/コア | 256KB/コア |

| 3次キャッシュ | 6MB | 8MB |

| 総容量 | 8.25MB | 9.125MB |

若干Phenom IIの方が総キャッシュ容量は少ないことになるが、Phenom IIは理論上この8.25MBをフルに利用できる。キャッシュ間で重複してデータを持つことがないので、総容量=利用可能容量となるためだ。それに対して、インテルの方は1次/2次キャッシュが3次キャッシュと重複してデータを持っている可能性が強く、結果として利用可能容量は8MB~9.125MBの間のどこかになる。AMDの方が効率がよい可能性があるわけだ。

それでも最近は、容量差が縮まったほうである。例えば2002年には、AMDは0.13μmプロセスの「Thoroughbred」コアのAthlon、インテルは同じく0.13μmプロセスの「Northwood」コアの「Pentium 4」をリリースしていた。2次キャッシュのサイズはThoroughbredが256KBに対して、Northwoodは512KBでほぼ倍にもなった。両者の製品を比較してみると、おおむね以下のような傾向がある。

- 同一プロセス同士の比較だと、AMDの方が2次キャッシュの容量が少ない

- インテルの方が1年程度、より微細化したプロセスの製品を早く投入する

- CPUコアそのものはAMDの方がやや複雑=トランジスタ数が多く、同一プロセスならダイサイズがやや大きい

性能改善だけを考えれば、Inclusive Cache構成の方がメリットがある。だが、これを採用しながら、インテルと同程度の2次キャッシュ容量とした場合、AMDの製品はインテルの製品よりもダイサイズがずっと大きくなる。つまり原価が高くなるという状況になるわけだ。

これは価格競争面では不利なので、同程度のダイサイズまで抑えるためには、キャッシュ容量を低めに抑えるしかない。そうなると今度はキャッシュ容量不足になるので、これをカバーするためにExclusive Cacheとして効率的な利用を目指す、というのがAMDのとった戦略だ。これは、インテルより先に微細化したプロセスを利用できるといった状況が訪れない限り、基本的には変わらない方針であろう。企業の競争力や置かれている状況が、キャッシュの構成にも影響を及ぼす、という非常にわかりやすい例と言える。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ