キャッシュの容量はトランジスター数と演算性能との

トレードオフで決まる

ここまでで、大雑把にキャッシュそのものの動作原理の説明は終わったので、ここからは性能改善という観点で論じていこう。

x86系で最初にキャッシュを内蔵した「Intel 486」シリーズの場合、8KBのユニファイドキャッシュを内蔵した(その後ライトバックをサポートした時点で、16KBに増量)。前回触れたとおり、キャッシュはメモリーアクセスの遅さを遮蔽する働きがある一方で、トランジスター数に大きなインパクトを与える問題もある。

特にIntel 486は、当初1.5μm(1500nm)という大きなプロセスを使っていたから、利用できるトランジスター数は限られていた。こうなると、キャッシュに大量のトランジスターを割くのと、それを減らして演算器の性能を高めるのとで、どちらが賢明かというのは非常に難しい問題となる。

x86の歴史を見る限り、少なくとも「Coppermine」(Pentium III)とか「Thunderbird」(Athlon)の時代までは、「キャッシュは最小限に留め、演算性能を高めるほうにトランジスターを割く」という方向性が明確だった。実際、Intel 486は8KBないし16KBのユニファイドキャッシュのみ。次の「Pentium」の時代でも、合計16KB(命令8KB/データ8KB)のままだった。

「MMX Pentium」になって、プロセスの微細化もあって若干利用できるトランジスターが増えたために、ようやく合計32KB(命令16KB/データ16KB)に増えるが、これに先立ってリリースされた「Pentium Pro」は、16KB(命令8KB/データ8KB)のまま。これがMMX Pentiumと同じ合計32KBに増量されるのは、「Pentium II」になってからだ。つまりこのあたりまでは、CPU内部に大容量のキャッシュを搭載するよりも、演算パイプラインの充実にトランジスターを費やすほうが、性能が上がりやすかったということになる。

とは言っても、8KB~32KB程度の1次キャッシュでは効果が知れているのも事実。これを補うために、マザーボード側に2次/3次キャッシュを搭載するとか、CPUパッケージ内ながらオフチップで2次キャッシュを搭載するといった形で補うことが、「Katmai」ベースのPentium IIIや「K7/K75」コアのAthlonの時代までは続いた。実はこの方式は、コンピューターの世界では昔からある「記憶装置の階層構造」という考え方にもかなう方式である。

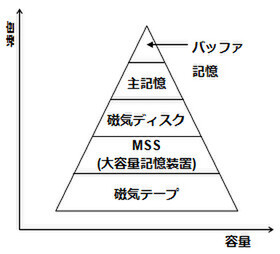

これは元々メインフレームなどの話で、図5-1のようなものである。ピラミッドの下の階層ほど容量が大きいが、低速である。階層が上がるにつれてどんどん速度は向上するが、その分容量が減り、かつしばしば高価になる。

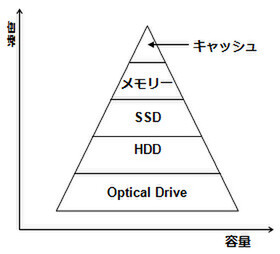

PCの場合は図5-2のように置き換えて考えるとわかりやすい。光学ドライブはメディアを入れ替えれば理論上無限の容量があり、対してHDDはどんなに大容量といっても限界がある。SSDはHDDよりずっと高速だが容量はHDDにまだ及ばないし、価格面では勝負にならないほど高い。メモリーはSSDと比べてもさらに高速かつ高価であるが、容量は数桁少なくなる。キャッシュはさらに少ないが高速である。

この階層構造は、「こうした特性を踏まえてシステム設計を考えましょう」ということでもある。大量のデータを処理するにしても、何度も全データを総なめするような処理の仕方をすると、結局一番遅い記憶装置の速度で処理時間が決まってしまう。だがこれを細かく分割して、その中でなるべく処理すれば、より高速な記憶装置が利用できるから、処理性能が上がることになる。

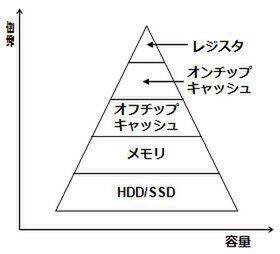

図5-3 CPU内~仮想メモリー(ストレージ)の階層

これはCPUの内部でも同じ話である。CPUの場合は図5-3のような構成になるだろう。1番下にHDD/SSDがあるのは、昨今のx86 CPUでは間違いなく仮想メモリーをサポートしたOS上で動作するので、プログラムから見ればメモリーとHDD(仮想メモリー)はほぼ等価である。

もちろん速度は大違いだ。毎回CPUがストレージにアクセスしていたら、例えSSDであろうとも、その動作ははてしなく遅くなる。そこで、HDDなりSSDから内容をメモリー上に展開して、普段はそこへアクセスする。しかしこれでもまだ遅いので、そのうち一部をオフチップキャッシュに、さらにその一部をオンチップキャッシュにそれぞれ展開し、その中で今まさに処理に利用するもののみを、レジスターに移してアクセスするわけだ。

この図式からもわかるとおり、必要なデータの移し変えをうまくやれば、必ずしも巨大なキャッシュをCPU内部に持つ必要はないことになる。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ