プロセスの進化にともなうリーク電流の増大で

省電力・発熱低減が現在の注目点に

むしろ昨今は、消費電力やそれにともなう発熱をいかに抑えるか、に力点が置かれつつあるのは、ご存知のとおりである。そもそも一般にCPUの性能は、以下の式で示される。

- Performance=Frequency×IPC

Performanceは一般に性能であり、Frequencyは動作周波数、IPCはInstructions Per Cycleの略で、ようするに「CPUが1サイクルあたりに処理できる命令の数」である。性能を上げるには、この両方を引き上げることで実現するわけだ。

ところがIPCの方は、そう簡単に引き上げられるものではない。元々x86の命令セットは、同時に複数の処理を並行して実行することを考慮したアーキテクチャーにはなっていない。一方これを当初から考慮したものとしては、インテルのItaniumとか、TransmetaのCrusoe/Efficeonなどに代表される、VLIW方式のアーキテクチャーが有名だ。

x86 CPUで同時に複数命令を実行するためには、CPUの側でプログラムの意味解釈に近いことをする必要がある。これは相当に難しく、世代ごとに「わずかずつ」IPCが向上しているものの、やっと3命令/サイクルが安定して出せる程度に向上した程度に過ぎない。Pentium 4世代のように、むしろ大幅にIPCが落ち込んだ世代もある。

あくまでも目安であるが、例えばi486DX-100の処理性能は45DMIPS(Dhrystone MIPS)程度だから、クロック当たり性能はおおむね0.45DMIPS/MHz。対して最新のCore i7シリーズの場合、Core i7-980X上でシステム診断ソフト「Sandra 2010」を使った際のDhrystone ALU値が103.5GIPSといったところだ。3.3GHz動作で6コア、2スレッドであることを考慮すると、1コア/1スレッドあたりの性能は2.59DMIPS/MHzという計算になる。

同一周波数で比較した場合、最新のCore i7はi486DX-100と比較して約5.8倍もIPCが向上した、という計算になる。だが、同じ期間に動作周波数は100MHz→3.33GHzと33倍も向上しているわけで、これだけ見てもIPCを向上させるのがいかに大変か(あるいは動作周波数を上げる方が簡単か)がおわかりいただけるかと思う。

この辺りの事情があったからこそ、第61回で説明したように、インテルがNetburst ArchitectureでIPCを犠牲にしてまでも、周波数を引き上げる方向に振ったのだと思われる。Netburst Architectureは「まず動作周波数ありき」と言わんばかりのアーキテクチャーと実装だ。それだけでは本当にIPCが下がりまくってしまうため、トレースキャッシュを初めとする多くのメカニズムで「IPCが下がりきるのを防止する」(向上させているとはとても言えない)という、ある意味大変に思い切りのいいアーキテクチャーになっていた。

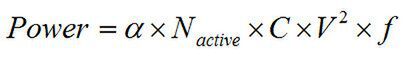

この路線がうまく行かなかったのは、(これも61回でも書いたとおり)消費電力の問題である。従来、消費電力は大雑把に言うと、以下の式1のように捉えられていた。

式1

- α:動作率

- Nactive:稼動するノードの数

- C:各ノードの負荷容量

- V:ノードに掛かる電圧

- f:動作周波数

消費電力は電圧が2乗で効くうえに、動作周波数もそのまま効いてくる。ただ、従来はCにあたるノードの負荷容量が、プロセス微細化にともない減っていたため、これと動作周波数向上がほぼ相殺するような形で維持されたことで、結果としてそれなりに高速動作が可能になってきていた。ところがプロセスが130nmを切って90nm世代に入ったあたりで、リーク電流の問題が出てきた。

リーク電流、日本語にすれば「漏れ電流」だが、ようするにトランジスターを小型化、薄型化しすぎた結果として、トランジスターの構造を乗り越えて電流が流れてしまう状況である。例えは悪いが、トランジスターを水道のパッキングと考えてみよう。パッキングが厚いと水は漏れないが、水道の開け閉めに時間が掛かる。そこでパッキングを薄くしていった結果、開け閉めは迅速にできるようになったが、閉めた状態でも水が漏れ出すようになってしまった、というあたりだろうか。

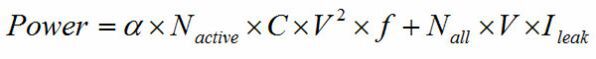

もちろん、漏れる量は水道を開けたときに比べればまだ少ないので、開けたか閉めたかは水量から区別できる。だが水道代という観点で言えば、無視できない量が無駄に流れ出ているといったところだ。この結果、消費電力の式は式2のようになった。前半は式1と同じだが、後半は以下のようになっている。

式2

- Nall:(CPU内で通電している)全ノードの数

- Ileak:リーク電流

ノードひとつあたりのリーク電流はそれほど多くないが、高速化・高機能化のために膨大なトランジスターを集約しているCPUの場合、トータルでの消費電力は馬鹿にならない。最終的にインテルの90nm世代Pentium 4の場合、リーク電流に起因する消費電力は、全体の30%近くに達したと言われている。こうした問題により、動作周波数向上一辺倒だったそれまでのアーキテクチャー進化の方向性は変わることになった。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ