MCMでは4プロセッサー構成のサーバーが作れない?

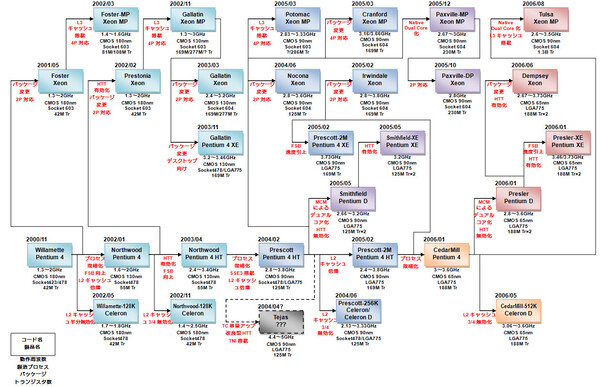

次の問題は「MCMをどうするか?」である。もともとインテルは386の時代から、共有バス方式のFSBをずっと使ってきた。これにより、Pentiumの頃からデュアルCPU構成が実現できたし、Xeon系列での2/4プロセッサー構成も容易だった。

もちろんデメリットもある。FSBは共有バス形式だから、複数のCPUが同時に通信することは不可能で、CPUの数が多くなると実効転送速度が落ちやすかった。また電気的にも、複数のCPUがあると信号波形が乱れやすくなるため、バス速度を引き上げにくい。

こうした問題点を鑑みて、インテルではCPUは最大4つまでとし、また2/4プロセッサー構成ではバスの性能が落ちる分は、大容量キャッシュをパッケージ内に搭載することで、なんとか埋め合わせをしていた。Xeon MPに4MBや8MBという大容量3次キャッシュが搭載されたのは、こうした共有バスにまつわるデメリットを最小限にするための方策だったわけだ。

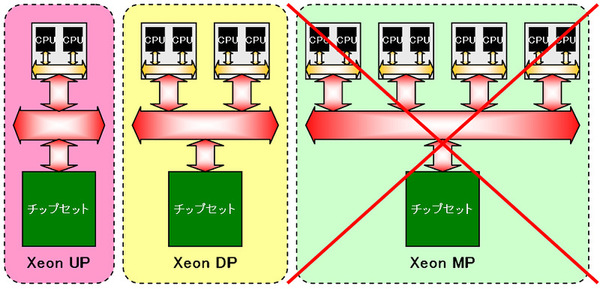

では本題に戻ろう。デスクトップ向けCPUはMCM構成を使ったデュアルコアCPUという形で性能を確保できたが、問題は2/4プロセッサー構成がデフォルトのXeonだ。例えば2プロセッサーの場合、物理的にはCPUは2つだが、内部は2つのコアが共有バスで結ばれる構造になっているから、電気的には4プロセッサー扱いとなり、FSBの速度を落とさないと動作しなくなる(詳細は関連記事参照)。

もっとキツイのは4プロセッサー構成。こちらは電気的には8プロセッサー構成になり、インテルのFSBの制約に引っかかるのでそもそも動作しない。特に4プロセッサー向けのXeon MPが大問題であった。

最終的にインテルは、MCMではない1ダイでのネイティブデュアルコアCPUを「Paxville-MP」としてリリースするが、これは元になったPrescottの発売から1年8ヵ月後の2005年12月のことであった。それまでの間、Xeon MP向けはシングルコアの製品しかリリースできなかった。このPaxville-MPには2次キャッシュ1MB版と2MB版が混在しており、このうち2MB版は、2005年10月に2プロセッサー向けのXeonとしてもリリースされている。

さらにインテルは、2プロセッサーシステム向けにもっと力技の解決策も用意した。これが2006年6月にリリースされた「Intel 5000」シリーズチップセットで、チップセットからFSBが2本出るというものだ。これならMCM構造のCPUでも、各FSBの先に1個(2コア)ずつ取り付ければFSBの制約はないようなもので、フルスピードで動作させられる。これにあわせて、Preslerをベースにした「Dempsey」コアが、Xeon向けに2006年6月にリリースされている。

それでは同じ発想で、「FSBを4本出せば4プロセッサー構成も……」となるのだが、これが実現するのはもう少し先の話となる。さすがにFSBを4本出すチップセットともなると、壮絶なピン数になるからだ。そのため、引き続きXeon MP向けは制約がついたが、これに合わせてCederMillをベースにネイティブデュアルコア化を図ったのが、2006年8月にリリースされた「Tulsa」である。こちらは最大16MBもの3次キャッシュを搭載し、最後のNetburstベースXeonに相応しいものとなった。

2006年にCore 2 Duoが登場すると、デスクトップ/サーバー向けともに、CPUは急速にCore 2ベースのものに置き換えられてゆく。最後まで残ったNetburst Architectureの製品は、CederMill-512KベースのCeleronであった。しかし、組み込み向けに長期供給体制がとられている品種もあるため、一応現時点でもオーダー可能で、その意味ではまだ製品寿命は残っているとは言える。

自作マーケットでは2008年あたりでほぼ消えてはいるが、メーカー向けとしては2009年も若干出荷されており、おおむね8年ほど使われたことになる。

今回のまとめ

・AMDのK7を性能で上回るべく登場したNetburst Architectureは、動作周波数を大きく引き上げることで全体の性能向上を図った。その第1弾である「Willamette」こと「Pentium 4」は、2000年11月に登場した。

・Pentium 4の普及期は、130nmプロセスにシュリンクした「Northwood」から始まる。NorthwoodはAMDのK8に対抗すべく、FSBの高速化やHTTの導入などの機能強化が図られた。

・Northwoodに続く90nmプロセスの「Prescott」は、リーク電流と発熱の増加に悩まされることに。次世代の「Tejas」は4GHz以上の性能を狙ったが、この問題を解決できずにキャンセルされた。

・K8につけられた性能の差を挽回すべく、MCMでのデュアルコアを実現した「Pentium D」を投入。しかしAMDもデュアルコアCPUを投入したので挽回できなかった。また、64bit拡張も導入されるが、当初計画したインテル独自方式ではなく、AMD64互換の方式を採用するはめに。

・サーバー向けCPUはさらに難渋する。特に、MCMでのデュアルコアCPUでは、既存のFSB方式のままでは2プロセッサーシステムで性能が低下し、4プロセッサーのシステムは作れない。解決にはネイティブデュアルコアの「Paxville-MP」が2005年末に登場するまでかかることになる。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ