SiSチップセットの歴史 その1

台湾御三家のSiS、ファブレス脱皮を目指して迷走す

2010年05月24日 12時00分更新

ラインナップは大幅縮小

他分野に手を出すもどれも迷走

もっともこうしたイケイケな勢いは、UMCによる事実上の吸収合併で雲散霧消する。ラインナップは大幅に縮小され、生産量も絞られることになった。またグラフィック部門はXGI Technology Inc.としてスピンアウトし、SiSはチップセットのみで再スタートを切ることになる。

その後も、インテルの高額なライセンス料や細かな条件縛り※1がきつく、一方AMD向けはNVIDIAやATIなどにシェアを奪われ、こちらも存在感が薄い状況で推移していた。

※1 2006年当時、SiSは組み込み向けや省スペースPC向けに、Pentium Mに対応したチップセットをリリースしようとした。しかし、ライセンスの関係でこれが許されず、やむなくPentium 4向けのみをリリースしたものの、これがさっぱり売れなかった。

これとは別に、1999年にSiSは、CPUベンダーのRiSE Technologyから、「m6P」コアのライセンスを受け、最終的には1999年末に同社を買収する。この資産を生かし、2000年には「SiS550」というCPU統合のSoCをアナウンスする。ところが、実際に出荷が始まったのは2001年に入ってからで、またSiSは自身でm6Pコアを改良することはついに行なわず(いや、行なえずか)、結局このビジネスも尻すぼみのまま終わってしまう。

その後は、「無線LAN市場に参入して2年後に撤退」とか、「USBコントローラーに参入するもほとんど売れず」とか、「メモリーチップとDIMMの販売を開始したけれど、ほとんどニーズがないまま扱い終了」など、傍から見ていると明らかに迷走している感が強かった。このあたりは次回以降で説明することにしたい。

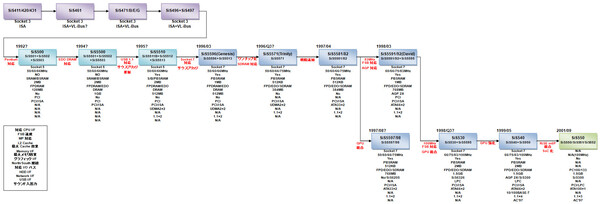

Socket 7対応製品は1992年頃から登場

今回はまず、SiSのSocket 7関連製品について解説しよう。正確な時期が不明なのだが、恐らく1992年あたりに、SiSは「SiS500」シリーズ(正確にはSiS501/502/503)という初のSocket 5向けチップセットをリリースする。これはVIAのApollo VP1と同様に、3種4チップによる構成となっている(SiS502が2つで、後はひとつずつ)。

このSiS500に続いて、ナンバーを1桁増やした「SiS5500」シリーズ(SiS5501/5502/5503)が、1994年か、ひょっとすると1993年にリリースされている。基本的な機能は変わらないが、EDO DRAMをサポートした点と、PLDB(PCI Local Data Buffer)と呼ばれる「SiS5502」が、1チップで済むようになったのが主な違いとなる。

続く恐らく1995年には、これの改良型である「SiS5510」シリーズ(SiS5511/5512/5513)がリリースされる。なぜかこのSiS5510では、2プロセッサー構成が可能になっているほか、サウスブリッジにパラレルATAが統合された。ただしこの時点では、サポートする転送モードはPIO Mode 4/UDMA Mode 2までで、最大でも転送速度は16.7MB/秒であった。

この改良型が「SiS5596」である。「Genesis」というコード名を持つこの製品で、ようやくノースブリッジが1チップ化された。さらにこのGenesisを、ワンチップ化したのが「SiS5571」である。「Trinity」と呼ばれるこの製品は、機能的にも75MHz FSBやSDRAMに対応する一方で、SiS5513の機能を全部取り込んだ結果、パッケージサイズはかなり大きなものになった。

これをさらに発展させたのが、「SiS5581/5582」である。この2つは機能は同じだが、ピン配置が異なるだけとなっている。機能的にはUltra ATA/33やACPIへの対応が追加された以外は、おおむねSiS5571と同等である。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ