年末年始特別編3

2011年の新CPUコア「Bulldozer」「Bobcat」の姿

2010年01月11日 12時00分更新

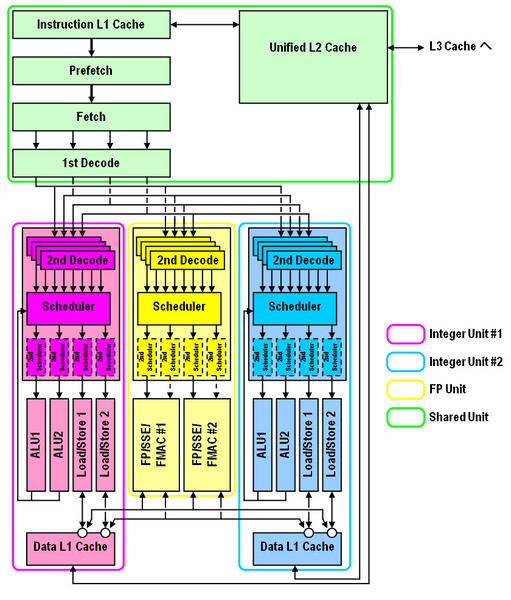

上の図は、スライドを元に筆者が推定したBulldozerの内部構造図である。まず2スレッドで共用となるレジスターファイルから、恐らく32Byte/サイクルの帯域でプリフェッチ~フェッチを経由してデコードユニットに取り込まれる。フェッチではx86を4命令/サイクルで解釈、これを4つの「MacroOp」に変換して、スレッド毎のスケジューラーに投入する。

各スレッドのスケジューラーは、恐らくMacroOpを2つのOpに変換する4対のデコード(2nd Decode)に投入して、その結果をまず第1段のキューに投入する。ここで実行ユニット別にOpをスケジュールしなおして、その結果を第2段のキュー(2nd Scheduler)に投入、その後各実行ユニットで順次処理する形になると思われる。

大きなポイントは、MacroOpの取り扱いである。従来のK7~K10では、例えばLoad命令+ALU命令をひとつのMacroOpとし、これをOpに変換後もそのままペアにしてALUとロード/ストアユニットに投入する形を取っていた。そのため、例えばLoad+ALUが連続するようなケースでも、3命令/サイクルが維持できる。ところが逆に言えば、Load命令3つとALU命令3つが並んでおり、これがそれぞれ独立してるなんてケースでは、ALUとロード/ストアユニットを同時には使えない。そのため、この6命令を処理するには2サイクル必要になり、実行ユニットは常に半分が遊んでいる形になる。

これがBulldozerの場合、Load命令とALU命令がペアになっているのは第1段のデコードの出力までで、第2段のデコードを経てスケジューラーに入る段階でこのペアが切り離される。しかもロード/ストアユニットはALUとは連動せずに動く。「4命令のアウトオブオーダー」はこの段階の動作を指していると思われる。この結果、Load+ALU命令であれば同時に2命令しか処理できないが、独立した3つのALU命令と3つのLoad命令であれば、実質1.5サイクルで処理できることになる。つまり、単純に「IPCが減った」と言い切れない構成に変わったわけだ。

加えて、2ロード/サイクルが可能というのは、つまり1次データキャッシュからのロードがピークで同時2命令処理できることになる。従来は、AGUは最大3つも並んでいたもののロード性能そのものは1ロード/サイクルだったから、例えば3つのLoad命令を発行しても実際に処理が終わるのはひとつだった。Bulldozerではこれが倍増したことになり、例えばLoad命令+ALU命令であっても、実質的なスループットはむしろK10よりも向上する可能性が高い。

ただし、単純なALU命令が続く場合は、当然ながらIPCは2命令/サイクルに留まるわけで、このあたりを勘案すると(当然アプリケーションによるが)若干ながら同一周波数あたりの性能は、K10世代より下がるのではないかと想像される。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ