年末年始特別編3

2011年の新CPUコア「Bulldozer」「Bobcat」の姿

2010年01月11日 12時00分更新

情報少ないBobcat その構造を予測する

最後にモバイル向けの新コア「Bobcat」である。2007年、当時AMDのCTOだったフィル・ヘスター(Phil Hester)氏に話を聞いたときには、「基本的には非常に単純なアーキテクチャーを用いる予定で、性能を引き上げるのに複雑なアーキテクチャー、例えば投機予測とか複雑な分岐予測とかを採用する予定はない」とのことだった。

ヘスター氏はさらに、「非常に小さく、トラディッショナルなx86コアだ。消費電力を抑えるような異なる実行ユニットを持つ、クラシカルだがハイレベルなx86コアだと言っておこう」と述べたが、実際に出てきたものは意外にも比較的新しい(アウトオブオーダーはすでに古典的技術なのかもしれないが)構造だった。

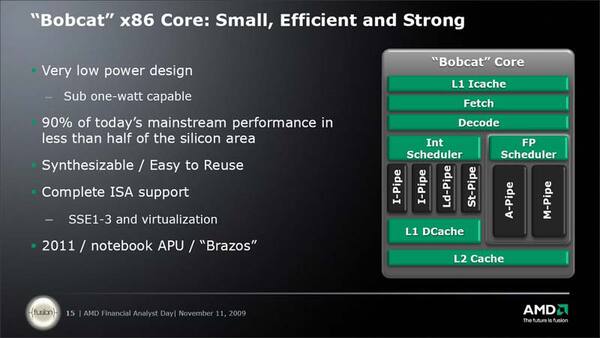

Bobcatコアの設計目標は、「1W未満の消費電力」と「性能をそれほど落とさずにダイサイズを半分に」というあたりである。先にPropusのダイサイズを約16.6mm2と紹介が、同じ45nm SOIプロセスならば約8.3mm2に抑えようというわけだ。

約8.3mm2という数字はかなり小さいように思うが、恐らくBobcatと競合するであろう他社の組み込み向けプロセッサーは、もっと小さい。例えば英ARM社の「Cortex-A8」は、65nmプロセスで3mm2未満、キャッシュを入れても4mm2未満とされており、45nmプロセスで作れば恐らく2mm2以下になるだろう。

もちろんARM並みまで縮小する必要はないだろうし、BobcatコアとGPUを統合したCPU「Brazos」の競合は、同じくAtomにGPUを統合した「Pineview」になるだろうから、逆に言えば「Atom程度の性能とダイサイズで収まれば十分勝負できる」という事になる。

さて、スライドから構造を見てみると、K7というよりもK6を想像するような構造になっている。インテルのAtomの場合、インオーダー・2命令発行ながら事実上1命令/サイクルとなるパイプラインを2GHzでまわしている。一方Bobcatの場合は、2命令/サイクルのアウトオブオーダーで恐らく2命令/サイクルとなるパイプライン構成となっており、動作周波数は1GHz程度になると思われる。

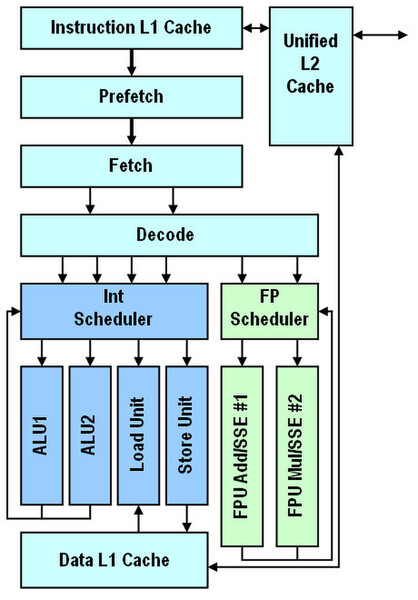

実のところ、BobcatについてはFinancial Analyst Dayでも、ほとんど解説がなかった(解説がBulldozerに集中していたため)が、構造からすると恐らく上図のような構造であろう。1次キャッシュ→プリフェッチ→フェッチは8Byte/サイクル程度で、デコードは2命令/サイクルで動作し、これを(MacroOpは使わずに)直接Opに変換する形になると思われる。

ALUは完全に独立で動くが、ロード/ストアユニットは(実行ユニットは分かれているものの)ひょっとすると同時には動かない(1次データキャッシュは同時1アクセスしかできない保守的なものになる)と思われる。FPUに関しては、64bitのADDとMULが分離されたものになり、SSE実行時には2つのパイプがそれぞれ動いて合計128bit演算を行なうものになるのではないかと想像する。恐らく、性能的には同一周波数の「K6-2」あたりよりやや落ちると想像される。分岐予測などのメカニズムはあまり搭載しないと思われるので、これによる性能低下が見込まれるためだ。

余談になるが、K6-2は0.25μmプロセスで135mm2程度のダイサイズだった。これを、単純に「プロセスが1世代進むとダイサイズが半分になる」と仮定すると、45nmでは8.4mm2程度になる計算だ。実際はここまできっちり半分にはならないから、もう少し大きく10mm2程度になるだろうか。だからといって、K6-2コアを引っ張り出してそのまま使うわけにはいかないのだろうが、Bobcatの目標と思われる8.3mm2に近いのは、なかなか興味深いところだ。

今回のまとめ

・2011年のCPUコア「Bulldozer」の構造を推測した。HTとは異なる仕組みで2スレッドを同時に実行できるほか、ALUとAGUの変更、MacroOpの扱いの改良により、同一周波数での性能は現行のK10世代より下がる可能性がある。

・構造変更の理由には、ダイサイズが関係するとみられる。K10まであった無駄を減らして、ダイサイズや消費電力を削減しようと考えたのではないか。同様に、2スレッド間でFPUを共有するのも、トランジスター数を節約してダイサイズ削減に貢献する。

・Bobcatに関する情報は少ないが、ARM系組み込みCPUやAtomへの対抗を目指す。古典的なコアをベースに、ダイサイズを約8.3mm2ほどに縮小する。分岐予測など複雑な仕組みは持たず、同一周波数ではK6-2世代よりやや性能で劣ると思われる。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ