Llanoの構成を予想する 内蔵GPUは480SP程度か?

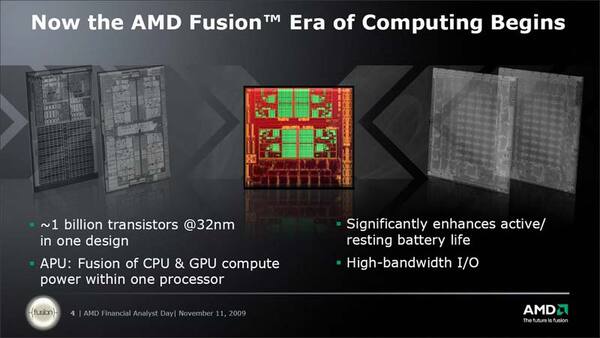

現時点ではFusionについての情報はあまり多くない。2009年のFinancial Analyst Dayで公開された情報をまとめると、以下のようになる。

- 全体が32nm SOIプロセスで製造され、総トランジスター数は10億個程度

- CPUコアはStars(つまり45nmのもの)ベース

- GPUはDirectX 11世代

とは言え、これだけからでもいくつかわかることはある。まずStarsコアの4コアとなると、ベースは今のAthlon II X4とそれほど変わらないと判断される。CPUコアについては、Athlon II X4のトランジスター数は約3億個、Phenom II X4では約7億5800万個と発表されているので、6MBの共有3次キャッシュ(と追加のHyper-Transport Link 3チャンネル分)が、両者の差の4億5800万トランジスターに相当することになる。

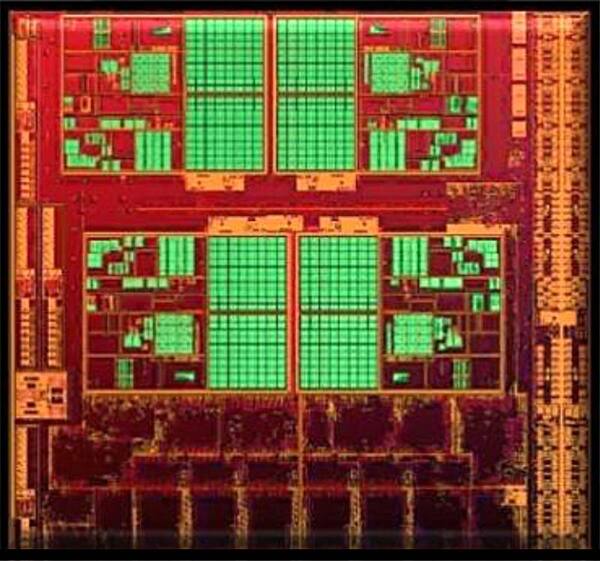

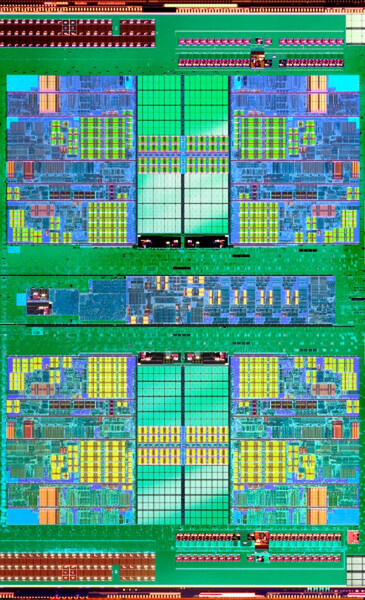

ではFusion(Llano)のCPUコアも、本当に3億個のままだろうか? 下の左写真は、上掲のスライドの中央部を拡大したもの。右写真はIstanburベースのOpteronのダイ写真から4コア分を切り抜いたものを示している。

Istanburは各コアあたり512KBの2次キャッシュを搭載しているが、2次キャッシュ部の幅はCPUコア部の3分の1よりやや大きい程度だ。一方で、Llanoは2次キャッシュ部の幅がCPUコア部の半分以上もあり、どうみても容量が異なっているとしか思えない。したがって、LlanoのCPUコアは、2次キャッシュをコアあたり1MB(合計4MB)ほど搭載している、と推定できる。

となると、その分のトランジスターのサイズがどの程度か? ということになる。ものすごく荒っぽい試算だが、例えば2次キャッシュも3次キャッシュも、構成するのに大きなサイズの違いがないと仮定する。その場合、6MB分の3次キャッシュ搭載に必要なトランジスター数がおよそ4億5800万個だから、コアの2次キャッシュを512KB増量(システム全体では2MB増量)するとなると、1億5300万個ほどトランジスタが増える計算になる。多少おまけをして1億6000万個とすると、CPUコア部のトランジスター数はおよそ4億6000万個というあたりだろうか。

ちなみに、本当はここに2チャンネル分のDDR2/3のメモリーコントローラーが統合されているが、これはFusionで新設したメモリーコントローラーと大きくは変わらない、と仮定しておく。となると、残る5億4000万個がGPUに割り当てられる計算になる。

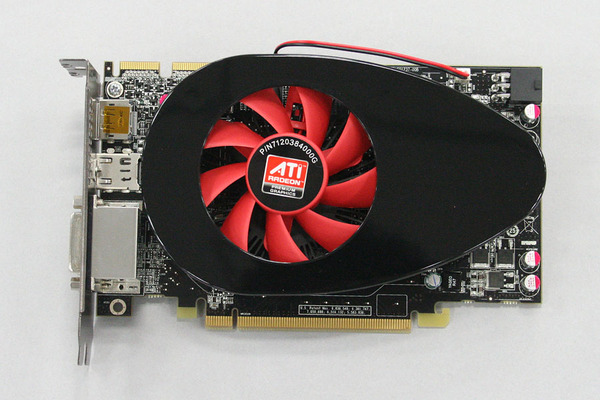

さて、次がGPUである。DirectX 11世代のGPUとしては、ハイエンドのRadeon HD 5870のトランジスター数が21.5億個(1600シェーダープロセッサー、以下SP)、それよりミドルクラスのRadeon HD 5770が10.4億個(同800SP)と発表されている。ここから引き算すると、800SP分で11.1億トランジスターとなって全然計算が合わない。だが、まずRadeon HD 5770はメモリーバスが128bitなのに対して、Radeon HD 5870は256bitなので、この分の差が含まれる。

また、Radeon HD 5870では大きく2つに分かれたシェーダブロックを内部的なCrossBarスイッチでつなぐ形になっているが、接続数がRadeon HD 5770の2倍になっているから、CrossBarの規模そのものは4倍(Crossbarの場合、2乗で効いてくる)になるため、この分が馬鹿にならないと思われる。

現実問題として以下のように見積もれば、おおむねトランジスター数は一致すると思われる。

- 800SPあたり8億個

- CrossBar部分は5770で1億個、5870で4億個

- そのほか(メモリーコントローラーやPCIeコントローラ)が1~1.5億個

これを当てはめると、5億4000万トランジスターならば540SP程度が収まる計算になる。ただし、Radeon HD 5xxxシリーズの場合、80SPをひとつの塊として扱っている。これをLlanoでも継承するとすると、560SP(80SP×7)ではちょっとはみ出す計算になるので、480SP(80SP×6)程度と考えたほうがよさそうだ。これなら以下の配分となる。残りはそのほかの用途で6000万個程度と考えればいいだろう。

- CPUコア+メモリーコントローラー 4億6000万個

- GPUコア(480SP) 4億8000万個

シェーダープロセッサーが480個という数字は、Radeon HD 5770の半分強であり、それほど高速とは言えないかもしれない。だが内蔵GPUとしては、かなり強力な部類に入るだろう。Radeon HD 5750/5770は、動作周波数が700~850MHzと比較的低速である。対してLlanoは32nm SOIプロセスを使うことで、もっと高速に動作する可能性が高いから、純粋にシェーダープロセッサーの性能だけで言えば、Radeon HD 5750に比肩しうる程度の性能が出るかもしれない。ただし、実際にはメモリーバス側がボトルネックとなる可能性があり、そこまでの性能は出ないのではないかと思われる。

今回のまとめ

・モバイル向けCPUロードマップは、2008年公表の情報から大きな変更なく進展した。2009年には45nm SOIプロセスのCPU「Caspiaon」も投入されたが、主流は65nm SOI世代だった。

・2010年には、モバイル向けCPUもDDR3ベースに移行する。メインストリームには「Champlain」、ウルトラポータブルには「Geneva」が投入される。

・2011年には、GPU統合型のFusionが、「Llano」「Ontario」として登場する。現時点では情報が少ないFusionだが、CPUコアの世代と総トランジスター数から推測すると、内蔵GPUはRadeon HD 5750以下の性能と思われる。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ