Intelチップセットの歴史 その5

DDR3に先鞭をつけたIntel 3~4世代のチップセット

2009年12月14日 12時00分更新

標準化を先取りしてDDR3対応チップセットを投入

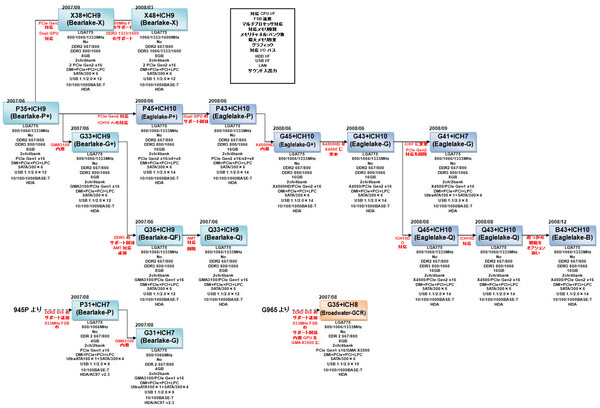

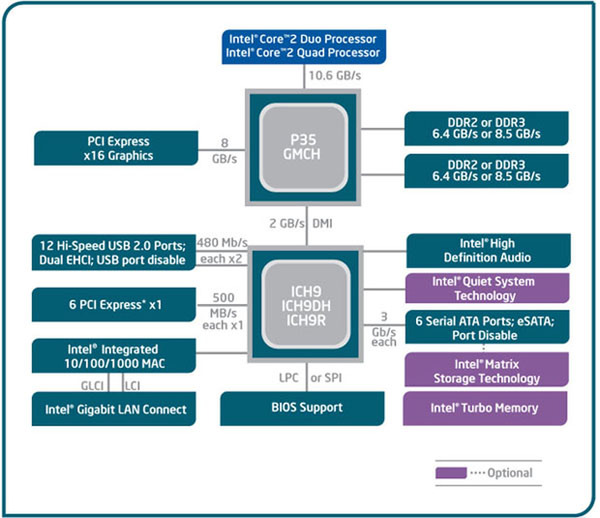

5回にも渡ったインテルチップセットロードマップ解説の最終回を始めよう。前回紹介したIntel 900ファミリーを3世代経たのち、ほぼDDR2メモリーが一般的になったタイミングで、インテルは新たにDDR3への移行開始を目論んだ。2007年6月にリリースされた「Intel P35」チップセットは、DDR2-600/800/1066に加えて、DDR3-800/1066/1333をサポートする、過渡期らしい構成のチップセットとなった。

Direct RDRAMではユーザーの支持を得られず、結果としてJEDECのロードマップのメモリーに戻ることになったインテルだけに、今回はJEDEC標準にあわせたというか、先取りするかのような動きとなった。これは別にメモリーだけの話ではなく、さまざまな標準技術についてインテルは、必ず標準化を先取りするような動きをとる事が多い。

標準策定後に製品開発に入ると、製品化する頃には一般化してしまっているので技術的な差別化が難しい。そうなると結局、その技術については価格競争になってしまい、儲けは少ない。対して標準化策定そのものから開発に携わっていれば、早期に製品を投入することで、高価格であっても「ほかにない」から購入してもらえる。

あるいは、早くから相互接続性を確認することで、安定した製品を出荷しやすい利点もある。例えばPCI Expressの場合、早期にテスター類を投入した計測器メーカーの米レクロイ社は、結果として高価格のアナライザーをそこそこに売ることができた。またインテルは、Intel 915シリーズ以前から、動作検証専用チップセットを投入していたために、グラフィックスカードとの相性問題が出ることはほとんどなかった。

ただし、こうした形で標準化をリードすることで早期投入を目指すことが、必ずしも必要ではない場合もある。例えばDDR2 SDRAMでインテルは早めに製品投入したものの、AMDやそのほかのベンダーが追従したのはずっと後だった。しかし、それによって後発各社がマーケットシェアを失ったとか、そういう話はない。ようするにAMDにとってDDR2メモリーは、「それが商品(CPU)の価値を左右するほど重要」とは判断しなかったという話である。

AMDがDDR2メモリーを採用したのは、Socket AM2プラットフォームを投入した2006年の事で、インテルに2年ほど遅れる形になっている。しかし、現実問題としてDDR2メモリーの価格がこなれてきたのがやっと2006年だから、これはむしろ時期に適った投入と判断された。逆に言えば、インテルは普及促進のためだけに、DDR2メモリーに早期対応したということになる。

この構図は、「Intel 3x」シリーズでも繰り返された。2007年6月に投入されたIntel P35は初のDDR3対応チップセットであるが、当時DDR3のメモリーモジュールなど数えるほどしか市場に存在せず、当然コストは高止まりだった。

この当時、DRAMベンダーは60nm台のプロセスでDDR3メモリーを製造していたが、これは動作周波数的にも消費電力的にも苦しいもので、またコスト面でも競争力がなかった。これらがこなれてくるのは、50nm台を経て40nm台の製造プロセスが使われる2009年に入ってからのこと。またもやインテルは2年も前倒しで、DDR3メモリーの整備のためにチップセットを市場投入したことになる。

おまけにこの時期は、DDR3メモリーを使う動機も乏しかった。FSBは800MHzから1066MHzを経て1333MHzに移行したが、1600MHzにはついにXeonと一部のデスクトップを除き移行しないままだった。必要とされるメモリー帯域は、1066MHzで8.5GB/秒、1333MHzでも10.7GB/秒に過ぎない。10.7GB/秒は、DDR2-667×2とちょうどマッチする帯域で、DDR2-800×2の12.8GB/秒はすでに過剰な規模である。この上メモリーを高速化するべき理由はどこにもない、という状況だった。

それでも、来るDDR3時代との橋渡しのために、DDR2とDDR3の両対応チップセットとして登場したのがP35だったというわけだ。ちなみに、組み合わせるICHは「ICH9」になっているが、細かく見ると、遠隔管理技術「AMT」(Intel Active Management Technology)を始めとする、企業向けクライアントプラットフォーム「vProテクノロジー」への対応などの違いがあるが、大雑把に言えばUSBが2ポート増えたのが、ICH8世代からの大きな違いである。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ