MCMでのデュアル/クアッド化にも問題が

Xeonが抱えたもうひとつの問題は、MCM(Multichip Module)構成である。図1では、ひとつのCPUパッケージにはひとつのCPUダイしか載っていないので問題なかったが、Pentium 4やCore 2では、MCMによるデュアルコア/クアッドコアCPUが登場した。こうしたマルチコアCPUを使った場合、実質的な構成は図2のようになる。

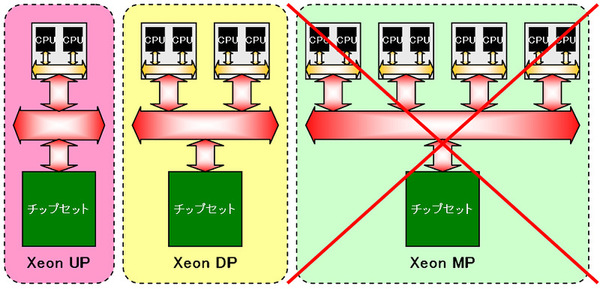

前述のとおり、P6バスやP4バスでは、CPUを最大4つまで接続できることになっているが、図2の構成だとXeon UPで2つ、Xeon DPでは4つ、Xeon MPで8つのCPUとなってしまい、事実上利用が不可能になる。そのため、Xeon DPがMCMを使ったクアッドコアCPUに移行した後も、Xeon MPはMCMを使わないデュアルコアCPUのみがラインナップされ続けるという時期が続いた。

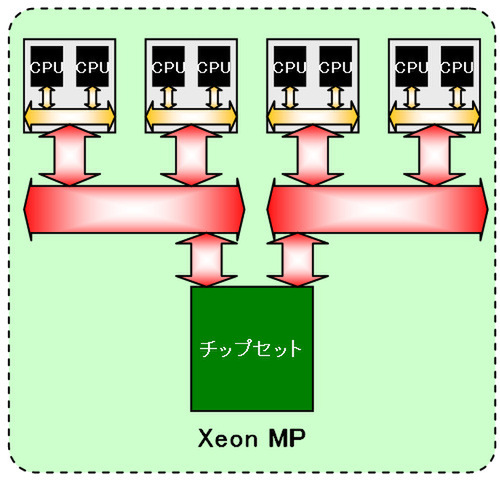

この問題について、インテルはXeon MP向けのみに、MCM構成を使わないデュアルコアCPU(Paxville-MP)やクアッドコアCPU(Whitefield)を開発した。しかし、Paxville-MPはXeon 7000シリーズ(7020/7030/7040/7041)として製品投入したものの、登場時期が遅かったこともあり、比較的短い製品寿命で終わってしまった。Whitefieldにいたっては、途中で開発中止となる始末だ。最終的には図3の様に、2本FSBを持つチップセットを投入することで、4ソケット構成を可能にしたが、もうこうなると共有バスである必要性そのものがあまりない。

ちなみに技術的には、チップセットの側で工夫することで、より多くのCPUを接続したシステムもある。実際に、チップセットメーカーのServerWorks社は、Pentium Proを6つ接続できるチップセットをリリース、これを使った製品も存在した。Corollaryという企業がリリースした、8CPUを接続できる「ProFusion」というチップセットも存在した(当時の米コンパック社が製品リリースを発表している)。

ただし、これらはいずれもP6バスの時代の話で、データレートの上がったP4バスの世代では、事実上4CPUが上限となっており、このあたりも共有バス方式のボトルネックと捉えられている。そんなわけで、Nehalemの世代ではついに共有バス方式のFSBを撤廃。「QPI」(QuickPath Interconncet)というまったく新しい接続方式を採用することになった。

(次ページへ続く)

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ