|

|---|

7月中にはOEM向けに出荷するとアナウンスされたインテルの次世代CPU“Conroe(コンロー)”。対応マザーボードも発売され、あとはCPUの正式発表と店頭販売を待つのみとなった。2.93GHzの「Core 2 Extreme」と2.66GHzの「Core 2 Duo」を元に、その性能を多角的に評価してみた。

IDFではFX-62を大きく上回る性能を実演

インテルは今回、Conroe投入にあたって、異例の“事前性能公開”を行なっている。最初は今年春のIDF(Intel Developer Forum)。月刊アスキーの誌上でもレポートしたが、ここで行なわれた特別セッションで、ほぼ同条件にそろえたConroe-2.66GHzとAthlon 64 FX-62相当機(Socket 939/DDRベースのAthlon 64 FX-60を2.8GHzにクロックアップしたもの)を並べ、各種ベンチマークでConroeが圧倒的に高速であることを見せつける内容を披露した。この時の結果はグラフ1のとおり。その後、6月には都内で再度ベンチマークセッションが開催されてもいる。

Athlonとしては、DDR2対応のSocket AM2モデルによってキャッチアップが期待されたが、Vol. 40で見たように、同クロックのSocket 939版に比べ、めぼしい性能向上が見られなかった。この点ではConroeが有利だが、ベンチマークセッションではインテルがセレクトし、インストールしたテストしか実行が許可されていないため、基本的にはConroeに不利なものは入っていないのは当然と考えられる。したがってここでは、本コーナー恒例のテストプログラム群において、Conroeが実際にFX-62以上の性能を本当にコンスタントに出せるのかが注目される。

|

| |

|---|---|---|

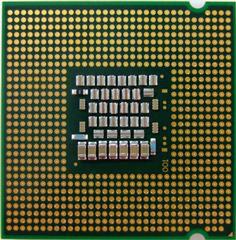

| “IDF 2006 Spring”でのベンチマークセッションでの結果のメモから。いずれも3Dゲーム。単位はfps、棒が長いほうが高速 | Core 2の裏面。パッケージ自体は現行のPentium 4と同じLGA775 |

“Conroe”=“Core 2 Duo”とは何か

“Conroe”ことCore 2 Duoの主な特徴は、すでに各所で解説されているが、性能に直結する部分と機能面で重要なものについてまとめると、以下の4点になる。

●共用の4MBキャッシュ

4MBもの2次キャッシュを1つのダイに内蔵している。これはPC用としては例を見ないゴージャスなものだ。Pentium 4 900番台は2MBのキャッシュを2つ、合わせて4MB搭載しているが、2MBキャッシュのCPUのダイを2つ乗せてくっつけたものだ。

●5命令解析&実行

CPUの性能は、クロック周波数と、1クロックあたりの命令実行数(IPC)に比例することはよく知られている。Core 2 Duoは、1995年のPentium Pro以来、ながらく変更がなかった「x86命令を3命令デコード、内部RISCエンジンで(デコード結果の)μopを5命令実行」というスペックを強化し、「x86命令を5命令、μopを6命令実行」とした。

歴史的にこれらがどのように変わってきたかを表にまとめてみた。80386では、2クロックにつき1命令の実行だったのが、486で1クロックに1命令となり、Pentiumで2命令、Pentium Proで3命令となったのが、今回ひさびさに増えたことがわかる。

Pentium IIIもCore DuoもAthlon(64)も、1次命令キャッシュからプログラムコードを読み取り解釈する能力(デコード)は1クロックにつき最大3命令だったのだが、Core 2 Duoではこれが5命令に増えている。この“入り口”の強化によって、1クロック当たりの実効平均命令実効数が大きく増えることが期待される。いくら命令実行ユニットがたくさんあっても、そこに命令を供給できなければ性能は上がらない。表では、CPUのポテンシャルとして、クロック周波数とデコード能力を掛け合わせた数値も並べてみた。

ちなみにPentium 4は、x86命令そのものを蓄えるキャッシュがなく、変換後のμopを1クロックにつき3つスケジューリングする構造だが、1つのx86命令は1つ以上のμopになるので、クロック当たり3μopsというスペックは、x86換算だともっと少なくなる。表のPentium 4欄でクロック×デコード数における“-α”はこれを意味している。

| クロック | デコード IPC(x86) | パイプライン IPC(μop) | 命令発行 IPC(μop) | 性能指標 (クロック×x86デコード) | |

|---|---|---|---|---|---|

| Intel 386 | 33 | 0.5 | 0.5 | 0.5 | 16.5 |

| Intel 486 | 100 | 1 | 1 | 1 | 100 |

| Pentium | 233 | 2 | 2 | 2 | 466 |

| K6 | 600 | 2 | 4 | 7 | 1200 |

| Pentium Pro~III | 1400 | 3 | 3 | 5 | 4200 |

| Athlon (XP) | 2200 | 3 | 3~9 | 9 | 6600 |

| Pentium 4 | 3800 | 3(μop) | 3 | 5 | 11400-α |

| Athlon 64 | 2800 | 3 | 3~9 | 9 | 8400 |

| Pentium M | 2266 | 3 | 3+α | 5 | 6798 |

| Core Duo | 2166 | 3 | 3+α | 5 | 6498 |

| Core 2 Duo | 2933 | 4+1 | 4+α | 6 | 14665 |

●メモリの投機読み出し

RISCエンジンにおける性能向上の大きな柱に、時間的に先の命令であっても実行可能であれば実行してしまう“逆順実行”機能がある。しかしメモリの読み出しについては、その前にメモリへの書き込み命令があった場合、先に読むと間違った値をロードしてしまう可能性があるため、従来は逆順実行できなかった。Core 2 Duoではこれを行なえるようになり、パイプラインのストール(停止)の大きな要因である“メモリの読み出し待ち”を大きく削減できるようになった。ちなみにItanium2やEfficeonでも類似の機能の実装例はある。

●スループット1のSSE命令

従来、Intel CPUではSSE命令のスループット(命令を発行可能な間隔)は2(2クロックにつき1つ)だった。これがCore 2 Duoでは1になっている。SSE命令が集中的に並ぶマルチメディア処理では、大きな性能向上が期待できる。

Core 2 Duoは、ベースとしてはCore Duoの延長にある。Core Duoでさえ、Pentium 4やAthlon 64 X2のミドルクラスの性能であるのに、1命令当たりの実行可能命令数が劇的に増え、メモリレイテンシの影響を受けにくくなり、マルチメディア処理が高速化し、クロックも最大36%アップするのだから、考えてみればぶっちぎりの性能が出ても当然といえる内容だ。以下、実際の検証結果をお届けしよう。