|

| |

|---|---|---|

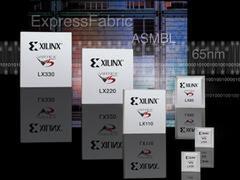

| 6タイプ中3タイプがサンプル出荷を開始した『Virtex-5 LX』プラットフォーム | Virtex-5の特徴について説明する、米ザイリンクス アドバンスト・プロダクツ部門プロダクト・マーケティング部長のチャック・トラルカ氏 |

ザイリンクス(株)は16日、65nmプロセスで製造するFPGAの新製品“Virtex-5”ファミリーを発表。Virtex-5 LXプラットフォームのサンプル出荷を開始した。従来のVirtex-4と比較して、平均30%の高速化を実現しながら、低消費電力化にも成功している。製造は(株)東芝の半導体製造部門であるセミコンダクター社と台湾United Microelectronics(UMC)社が担当する。

発表前に行なわれた記者説明会では、同社代表取締役社長の吉澤仁氏と米ザイリンクス社プロダクト・テクノロジ部門アドバンスト・プロダクツ・グループ担当副社長のヴィンセント・トン(Vincent Tong)氏により、日本およびワールドワイドでのビジネス概況が説明されたほか、ザイリンクス アドバンスト・プロダクツ部門プロダクト・マーケティング部長のチャック・トラルカ(Chuck Tralka)氏により、Viretx-5ファミリについての説明が行なわれた。

|

|---|

| ザイリンクス 代表取締役社長の吉澤仁氏(左)と、米ザイリンクス プロダクト・テクノロジ部門アドバンスト・プロダクツ・グループ担当副社長のヴィンセント・トン氏 |

ビジネス概況については、ワールドワイド・日本法人ともに売上は好調で、2006年1~3月期は過去最高の売上を記録したという。90nmプロセスで製造される同社のFPGA(Virtex-4、Spartan-3シリーズなど)は、3月時点で累積出荷個数が1200万個を突破するなど、順調に推移しているという。トン氏は同社のFPGA製品が好調な理由として、プログラマビリティーの高いFPGAを市場が求めていることを挙げ、競合他社の売上をザイリンクスが上回る原動力となっているとした。

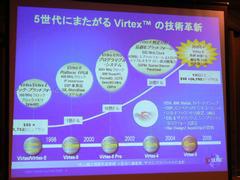

Virtex-5ファミリは、2004年に登場したVirtex-4をベースに、製造プロセスの微細化による省面積化と消費電力の低減、新技術の採用による性能向上を図ったシリーズである。以下の4種類のプラットフォームが用意される。

|

| |

|---|---|---|

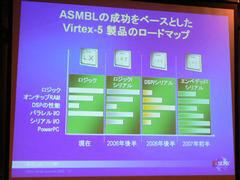

| Virtexシリーズのロードマップ。Virtex-4をベースに65nmプロセス化、高速化などを施したのがVirtex-5 | Virtex-5の4種類のプラットフォーム。シリアルI/Oの有無やDSP性能、組み込みCPU(PowerPC)などの違いがある |

- Virtex-5 LX

- 高性能ロジック向け:サンプル出荷中

- Virtex-5 LXT

- 高速シリアルインターフェースを備えた高性能ロジック向け:2006年後半サンプル出荷開始予定

- Virtex-5 SXT

- 高速シリアルインターフェースを備えた高性能DSP向け:2006年後半サンプル出荷開始予定

- Virtex-5 FXT

- 高速シリアルインターフェースと組み込みプロセッサーを搭載:2007年前半サンプル出荷開始予定

量産出荷時期については、LXは18ヵ月以内、LXT~FXTは6~9ヵ月後と予想されている。サンプル出荷中のFPGAは、Virtex-5 LX50、LX85、LX110の3タイプで、それぞれ5万、8万5000、11万のロジックセルを備える。内蔵ブロックRAM(BRAM)はそれぞれ、1728kbit、3456kbit、4608kbit。2008年の量産価格(1000個購入時)は、149ドル(約1万6330円)、279ドル(約3万578円)、399ドル(約4万3730円)と想定されている。またLX30、LX220、LX330の3タイプも6カ月以内に出荷可能になる予定で、LX330は33万ロジックセル、約10MbitのBRAM内蔵の予定。また最大1200本の“Select I/O”ユーザー端子を使用可能。

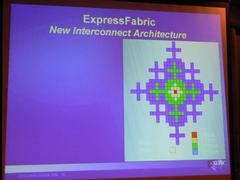

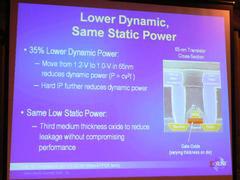

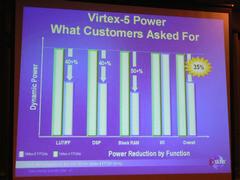

6つの独立した入力を持つルックアップテーブル構造を持つ“Express Fabricテクノロジ”を採用。内部の配線アーキテクチャーを斜め構造にすることにより、短く高速な配線が可能になるといった特徴も備える。これらによりロジック性能(速度)は平均で30%向上したとしている。また微細な65nm製造プロセスを採用することで、90nmプロセス世代と比べて45%の省面積化を実現しているほか、低消費電力化に適するトランジスター技術“第2世代のトリプル・オキサイド・テクノロジ”の採用や、1.0Vの電源電圧などにより、スタティック消費電力はそのまま、ダイナミック消費電力を35%低減することで、低消費電力化を実現している。

|

| |

|---|---|---|

| Virtex-4 | Virtex-5。斜め方向に対称とすることで、ホップ数を減らして遅延時間を短くするなどの利点を持つ | |

| Virtex-4とVirtex-5の配線アーキテクチャーの違いのイメージ図 | ||

|

| |

|---|---|---|

| トランジスター構造の顕微鏡写真を交えた、低消費電力化の説明スライド | ダイナミック消費電力の減少割合を示すグラフ。平均で35%の低消費電力化を実現するという |

記者説明会にはゲストスピーカーとして、製造担当の東芝 セミコンダクター社 技師長の衣川正明氏、Virtex-4を採用する光通信装置を開発した日本電気(株)ブロードバンドネットワーク事業本部支配人の陶山茂樹氏らが登壇。衣川氏はVirtex-5のエンジニアリングサンプルを製造した300mmサイズのウエハーを手に、65nm製造プロセスだけでなく次世代の45nm製造プロセスでの半導体製造に向けた研究開発が進んでいることを述べた。また陶山氏は、同社の光通信装置『DW4200』にVirtex-4を2基使用した40Gbps信号インターフェースの実装や、レイヤ2スイッチ製品『CX2600/220』にVirtex-4を採用した事例を紹介。さらに高速なFPGAへの期待を述べた。

|

| |

|---|---|---|

| Virtex-5製造に使う300mmウエハーを掲げる東芝 セミコンダクター社 技師長の衣川正明氏 | NECが開発した40Gbps級の信号インターフェースとそれを組み込んだ光通信装置の写真。Virtex-4を2基使い、40Gbps光インターフェース規格“SFI-5”をFPGAで初めてサポートした |