【IDF Spring 2006 Vol.1】なぜいま“マルチコア”なのか?――米インテルCTOのラトナー氏、基調講演にて技術的観点から疑問に答える

2006年03月08日 23時56分更新

|

|---|

| オープニングキーノートに登場した、インテル最高技術責任者のジャスティン・ラトナー氏 |

米インテル社が主催する開発者向け会議“Intel Developer Forum Spring 2006”(IDF)が、米国カリフォルニア州サンフランシスコ市内Moscone Convention Center Westにて7日(現地時間)に開幕した。初日には4本もの基調講演が行なわれたが、IDFのオープニングを飾る最初の講演では、米インテル社の最高技術責任者(CTO)であるジャスティン・ラトナー(Justin Rattner)氏が壇上に立ち、今後数年間の同社の技術フォーカスと、パソコン向けプロセッサーの将来像について語った。

インテルにとっての2005年は、大きな戦略転換点であると同時に、将来の技術開発やマーケティング面での大きなチャレンジの年でもあった。プロセッサーの高クロック化でつまづいた同社は、マルチコア化と複数の機能をプロセッサー内に取り込むことで、総合的なパフォーマンス向上を目指すようになる。2005年末には長年親しんできた“Intel Inside”のロゴを変更し、さらにプロセッサーのブランド名を“Pentium”から、デスクトップパソコン、ノートパソコンまでをカバーする“Intel Core Microarchitecture”という名称に変更するなど、マーケティング上の一大転換も行なっている。そんな同社が今後数年間の戦略的なキーワードとして挙げるのが、“Energy Efficiency(電力効率)”だ。

基調講演のスピーカーを務めるラトナー氏が2005年12月1日にCTOに就任した際、記者団を前にしたインタビューにおいて、「パフォーマンスだけでなく、消費電力やセキュリティーの問題も同時に解決しなければならない」と、今回の“Energy Efficiency”につながる戦略を打ち出していた経緯がある。ラトナー氏はプレゼンテーションの中で、Energy Efficiencyにつながる技術的バックグラウンドについて説明を行なった。

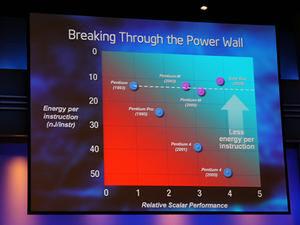

インテルはヒット商品となったPentiumの発売以来、プロセッサーの高クロック化に邁進してきた。結果として性能は上がったものの、1命令の実行にかかる電力の上昇も招いてしまい、Pentium 4の世代においてついに、発熱の問題から高クロック化を断念せざるをえなくなった。この転換点となるのがノートパソコン向けプロセッサー“Pentium M”の登場で、Pentium Mにより1命令あたりの電力消費を初代Pentium世代の水準まで落とし込むことが可能になった。同社の最新のデュアルコアプロセッサーであるCore Duoもまた、Pentium Mをベースに改良を行なった製品であり、初代Pentiumと同水準の電力効率を持っている。

|

|---|

| Pentium以降のインテルCPUのパフォーマンスと1命令あたりの電力効率のグラフ。Pentium Mの登場で、電力効率は初代Pentiumのレベルに戻った |

|

|---|

| オレゴン州にある、同社の45nm製造プロセスの実験棟 |

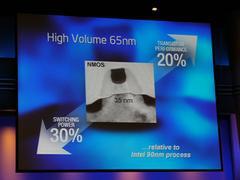

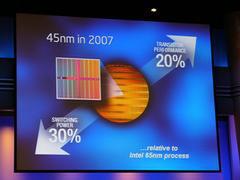

アーキテクチャーの改良以外で電力効率の向上に寄与するのが、プロセスルールの微細化だ。同社は2005年後半に、ノートパソコン向けCPUを中心に、従来の90nmから65nmの製造プロセスルールへと移行を済ませている。一般的にはプロセスルールが微細化すると、前世代に比べてパフォーマンスの向上と低消費電力化が容易になる。ラトナー氏の説明によれば、90nmから65nmへの移行により20%の性能向上と30%の電力効率向上が見込めるという。また同社では65nmの次の世代に当たる45nmプロセスにもすでに焦点を当てており、2007年には実験室のレベルを終えて、実際の製造に移れる見込みだという。現在同社は米国オレゴン州にある研究施設にて、45nmプロセスを使用したプロセッサーを製造可能な工場(Fab)の準備を進めているが、これを米国アリゾナ州やイスラエルなどにも順次拡大していく計画だという。45nmへの移行により、65nmと比較してさらに20%の性能向上と30%の電力効率向上が(理論的には)実現可能になる。

|

| |

|---|---|---|

| 業界に先駆けて、インテルは65nmプロセスでのプロセッサーの大量製造を実現している。これにより前世代と比較して、20%の性能向上と30%の電力効率向上が実現される | インテルは2年周期でプロセスルールの微細化を実現しており、2007年後半には45nmの大量製造に向けて動き出す。実験レベルでは、すでに32nm製造プロセスも視野に入っている |

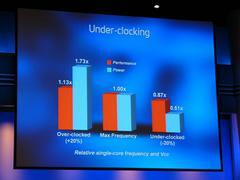

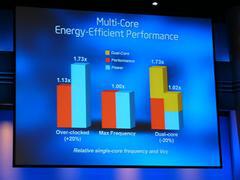

微細化の次に来るのがマルチコア化だ。ラトナー氏はスライドで、“なぜマルチコア化が必要か”を説明する。例えば、あるプロセッサーを20%ほどオーバークロック状態で動作させたとき、パフォーマンスは1.13倍向上するものの、電力消費は1.73倍にまで跳ね上がってしまう。ところが同じプロセッサーを、クロックを下げたアンダークロック状態で動作させるとおもしろい現象が発生する。20%のアンダークロック動作の場合、プロセッサーのパフォーマンスは通常時の0.87倍となるが、電力消費はなんと0.51倍にまで落とすことが可能となる。もしアンダークロック動作させたプロセッサーを2つ組み合わせれば、電力消費は通常クロック動作のプロセッサーと同程度ながら、およそ1.73倍のパフォーマンスを得ることが可能となる。これがマルチコアを採用する意義だと、ラトナー氏は述べている。

|

| |

|---|---|---|

| あるプロセッサーをオーバークロック/アンダークロック動作させた場合のパフォーマンスと電力消費の関係を示すグラフ | アンダークロック動作のプロセッサーを2つ重ねる(グラフの黄色部分)と、電力消費はそのままに、パフォーマンスだけを向上することが可能となる。これがマルチコア化の意義である |

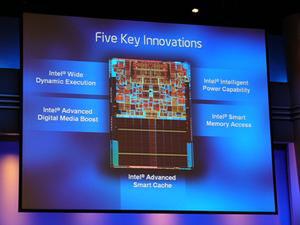

アーキテクチャーの改良とプロセス技術の微細化、マルチコア化に加え、さらにインテルは多くの技術を新プロセッサー開発に投入している。「新プロセッサー開発には何百もの新技術が投入されているが、この場ではあえて、そのうちの5つだけをピックアップして紹介しよう」とラトナー氏は述べ、以下の5つの技術を紹介した。

- Wide Dynamic Execution

- 4つの14段パイプラインで命令を効率的に実行する。

- Advanced Digital Media Boost

- 1サイクルで128bitのSSE命令が処理可能

- Advanced Smart Cache

- 共有型2次キャッシュ

- Smart Memory Access

- プリフェッチ動作の高度化で、メモリーアクセスのさらなる効率化

- Intelligent Power Capability

- より高度な消費電力管理

|

|---|

| 新プロセッサー開発に向けて投入された5つの代表的な技術 |

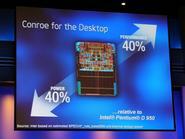

これら技術が結集して誕生したのが、2006年後半に登場予定の“Merom(メロン)”“Conroe(コンロー)”“Woodcrest(ウッドクレスト)”という3つのプロセッサーだ。ノートパソコン向けのMeromは、現在のCore DuoのCPUコアである“Yonah(ヨナ)”をさらに改良し、フルスクラッチで設計されたデュアルコアプロセッサーである。Core Duo T2600-2.16GHzと比較して20%の性能向上を実現しており、バッテリー持続時間もさらに向上しているという。デスクトップパソコン向けのConroeの場合は、現行のPentium D 950-3.40GHzと比較してパフォーマンスで40%、電力効率で40%の性能向上が見込まれる。またサーバー向けのWoodcrestでは、デュアルコアXeon-2.8GHz 2×2MBキャッシュ版と比較して、パフォーマンスで80%、電力消費で35%の向上が見込まれるという。

|

|

| ||

|---|---|---|---|---|

| ノートパソコン向けの“Merom” | デスクトップパソコン向けの“Conroe” | サーバー向けの“Woodcrest” | ||

| 各次世代CPUと現行CPUのパフォーマンス比較 | ||||

またインテルでは、2007年に“クァッドコア”と呼ばれる4つのコアを搭載したプロセッサーのリリースも計画しているという。クァッドコアプロセッサーは当初、サーバー向けを中心に展開されることになると思われる。またそれと平行して、マルチスレッド動作に必要となるソフトウェアの整備にも力を入れており、ソフトメーカー各社へのツールや技術の提供なども進めている。

|

|---|

| 実験システムの外観。グラフィックモジュールはチップセットから独立しているため、システムがアイドル状態になると動画再生は静止するが、ディスプレー表示だけは行なわれている |

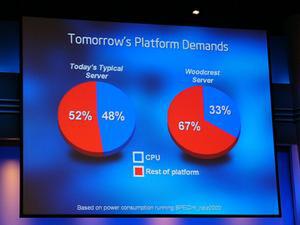

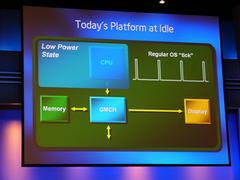

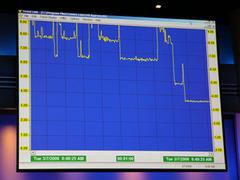

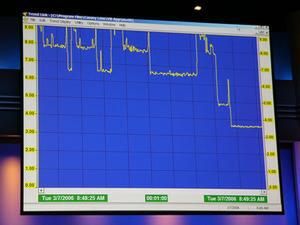

ラトナー氏は講演の最後に、1つのデモを披露した。同氏の説明によれば、現状のサーバー向けプラットフォームではCPUと周辺モジュールの電力消費の比率はほぼ1:1と均衡しているが、これがWoodcrestの世代になると、CPUが1に対し残りが2倍と大きく差が開くことになるという。プラットフォーム全体の電力効率向上を目指すのであれば、この差は見過ごせない。ラトナー氏が披露した実験システムでは、CPUがアイドル状態にあるとき、CPUだけでなくチップセットとメモリーの両方を含めてアイドル状態にすることで、電力消費をさらに押さえ込むことが可能になっている。デモでは7~9Wの範囲で動作していたシステムが、この新しいアイドル状態を維持する技術により、4W近くまで消費電力を落とすことを可能にしていた。CPUだけでなく、プラットフォーム全体での電力制御の重要性を訴えたデモと言えるだろう。

|

|---|

| 現状のサーバーシステムと、Woodcrest世代のCPUおよび周辺モジュールの電力消費比率 |

|

| |

|---|---|---|

| 現状のシステムでは、省電力モードはCPUのみがアイドル状態になる | 実験システムでは、メモリーやチップセットも含めてアイドル状態になり、さらに消費電力を落とすことが可能になる |

|

|---|

| 活動~アイドル状態を繰り返していた実験システムが、新技術によりメモリーなども含めてアイドル状態になったことで、4W近辺まで消費電力を低減させたことを示すグラフ |