【IDF Spring 2006 Vol.0】“Intel Developer Forum Spring 2006”開幕!――米インテル、メニイコア時代の課題を解決する“Tera-Scale Computing Research Program”を発表

2006年03月07日 15時41分更新

|

|---|

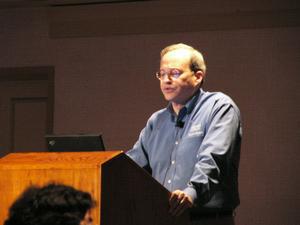

| 2005年12月にCTOに就任したばかりのジャスティン・ラトナー氏。CTO就任後に公の場で講演を行なうのは、今回が初めての機会 |

米インテル社が主催する開発者向け会議“Intel Developer Forum Spring 2006”(IDF Spring 2006)が、7日から9日(以下日付は現地時間)まで、米国カリフォルニア州サンフランシスコにて開催される。IDFは毎年2回開催されており、同社の最新技術や製品ロードマップの動向や、ハードウェア/ソフトウェアの実装方法など、同社の最新情報が続々と公表される大規模な国際会議である。数回に渡ってIDF Spring 2006の模様をレポートする。

インテルはIDF Spring 2006開催に先立つ6日に、テラバイト級のデータ処理を可能とするプロセッサー開発を目指した研究プロジェクト“Tera-Scale Computing Research Program”を発表した。同プロジェクトは80以上の関連プロジェクトで構成され、世界中にいる同社の研究者数百人が研究開発に従事しているという。プロジェクトのゴールは、現状のデュアル/クァッドコア(4コア)をはるかにしのぎ、“Many Core(メニイコア)”と称される10~100のコアを搭載したプロセッサーを開発し、テラバイト級のデータ処理能力を有するテラ世代のコンピューターを実現することにある。

この発表は、同社最高技術責任者(CTO)のジャスティン・ラトナー(Justin Rattner)氏が報道関係者を前に行なわれた。ラトナー氏は「命令レベルの並列化や高クロック化の限界に突き当たったインテルにとって、プロセッサーのマルチコア化は大きな方針転換とチャレンジになる。ここから得られる低消費電力と高パフォーマンスというメリットを生かし、来たるべきテラ世代のコンピューターを実現していく」と、その背景について説明している。

だがTera-Scale Computingへの課題は多い。コアの数が増えることで同時処理可能なスレッドの数は増やせるが、プロセッサーにはスレッドの効率的な処理が要求されるだけでなく、I/Oやメモリーの広帯域化、高度な電力制御などが必要となる。またマルチスレッドに最適化されたソフトウェア側の整備も必要となるだろう。

同社では多スレッド化の弊害の例として、メモリーの“ロック問題”を挙げている。現在のプロセッサーでは、あるスレッドがメモリーにアクセスしている間、そのメモリーはロック状態となって他のスレッドからはアクセスできなくなり、ロック状態が解除されるのを待たなければならない。これはマルチスレッドのメリットを損なうだけでなく、処理効率を落とし、ひいてはシステムのデッドロックやエラーを引き起こす原因ともなる。ラトナー氏は火星探査ロボットの“Mars Rover”が、このメモリーロック問題でフリーズした例などを挙げた。この解決策として研究が進んでいるのが“Transactional Memory”と呼ばれるもので、複数スレッドの同一メモリーへの同時アクセスを実現し、並列性の向上やデッドロック状態の削減を目指す。

これらのように、“半導体”“プラットフォーム”“ソフトウェア”の3つの分野で、テラ世代プロセッサーの課題を解決するための80以上の技術プロジェクトを集めたものがTera-Scale Computing Research Programというわけだ。「マルチコアを実現する半導体技術、最適化されたプラットフォーム、マルチスレッドに最適化されたソフトウェアの3つの組み合わせにより、Tera-Scale Computing世代への“ロケットジャンプ”が可能になる」とラトナー氏は述べている。