インテル、“テクノロジ・ショーケース”にて、日本初の次世代デュアルコアCPUのデモなどを披露――サーバー&ワークステーション向けCPUもデュアルコア化が進む

2005年06月08日 22時10分更新

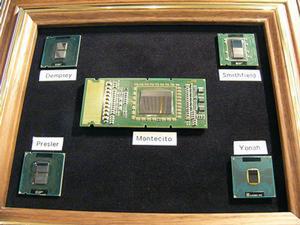

インテル(株)は8日、千葉市美浜区のホテルニューオータニ幕張にて、同社の最新製品を搭載したサーバーシステムや、開発中のCPUなどを展示する“インテル テクノロジ・ショーケース”を開催。開発中のデュアルコアCPU“Dempsey(デンプシー)”の日本では初公開となるデモを披露するなど、同社のデュアルコアCPU戦略についての講演を行なった。このイベントは、8日から幕張メッセにて開催されているインターネット関連製品展示会“Interop Tokyo 2005”に合わせて開催されたもので、業界・報道関係者だけでなく、一般の来場者も観覧可能であった。

|

| |

|---|---|---|

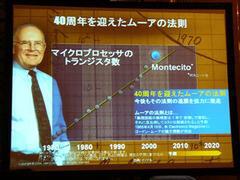

| インテル エンタープライズ&ネットワーク・ソリューションズ本部 プラットフォーム&ソリューション 統括部長の平野浩介氏 | ムーアの法則は継続されているとするスライド。Montecitoはトランジスター数が17億個にもなるという |

ショーケース会場に併設されたセミナースペースで行なわれた講演では、同社エンタープライズ&ネットワーク・ソリューションズ本部 プラットフォーム&ソリューション 統括部長の平野浩介(ひらの こうすけ)氏により、同社のプラットフォーム戦略について、改めて説明が行なわれた。インテルの元会長であるゴードン・ムーア(Gordon E. Moore)氏が提唱した半導体製造技術の進歩についての法則“ムーアの法則”は、今年で40周年を迎える。平野氏は現在でも同社はムーアの法則に則したペースでの技術革新を遂げており、今年投入予定のマルチプロセッサーシステムシステムデュアルコアCPU版向けItanium、コード名“Montecito(モンテシト)”では、90nm製造プロセスでトランジスター数は17億個にも及ぶという。プラットフォーム戦略自体は、特に新しい話題はなかったが、IA-64アーキテクチャーのItanium 2シリーズに加えて、XeonやPentium 4も64bit拡張技術“EM64T”をサポートしたことにより、今年中にすべてが64bitに移行するとした。またハードウェア仮想化技術“インテル バーチャライゼーション・テクノロジ”(VT)は、CPU側での実装が進むことで、今年にはサーバープラットフォームでの実用が始まるだろうと、平野氏は述べた。

|

|---|

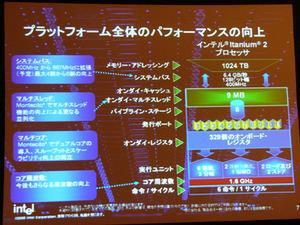

| Montecitoで実装されるItaniumの拡張点とおおまかなブロックダイアグラム |

Itaniumシリーズの普及と拡張について平野氏は、世界全体では昨年より3倍の売上金額の成長を実現しており、米Fortune誌のGlobal100に名を連ねる100社のうち、60社がItaniumサーバーを導入しているとした。そのうえでMontecitoでの拡張点について述べ、デュアルコア化に加えてマルチスレッド対応や、現在400MHzのシステムバス周波数の667MHzへの高速化などを挙げた。それに続いて、Itaniumベースのサーバープラットフォーム“BladeSymphony(ブレードシンフォニー)”を展開している(株)日立製作所 エンタープライズサーバ事業部 第二サーバ本部 本部長の秋本一泰(あきもと かずやす)氏が登壇し、BladeSymphonyで使われている日立のサーバ技術について述べた。

|

|---|

| 日立製作所 エンタープライズサーバ事業部 第二サーバ本部 本部長の秋本一泰氏 |

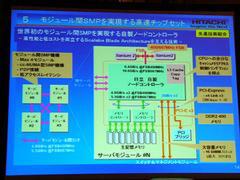

秋本氏はBladeSymphonyで使用されている日立製のチップセットについて触れ、高メモリースループットと低メモリーレイテンシーを重視し、PCI Expressのような最新I/O技術や、VTと日立製ソフトウェアによる仮想化技術もサポートしているとした。またMontecitoにもすでに対応準備を終えており、システムバス帯域の拡張によるメモリーアクセスの高速化は、大規模データベースアプリケーションなどに最適であると述べた。なおBladeSymphonyについては、こちらの記事を参照のこと。日立で行なったテストでは、メモリーアクセス速度を測定するベンチマークテスト“STREAM Benchmark”の測定結果で、最大40%の高速化を達成したという。

|

| |

|---|---|---|

| Monteticoに対応する日立製のサーバーモジュールの特徴。システムバスの高速化により、メモリーアクセス速度に大きな改善が見られるとしている | 左のサーバーで利用される日立製チップセットのブロックダイアグラム。4つのモジュール間の接続に、クロスバーではなくピアツーピアの方式を採用し、他のモジュールへのアクセスで発生するレイテンシーを短縮しているという |

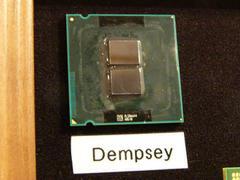

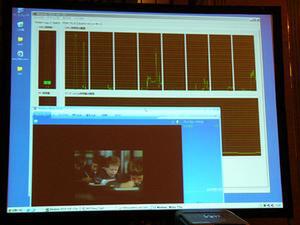

続いて平野氏は、日本初公開という次世代のデュアルコアXeonであるDempseyを使用したデモを披露した。デモと言っても非常に単純なもので、2つのDempseyを搭載したペデスタル型のサーバー上でWindowsを実行し、その上でビデオを再生してみせた程度であった。Dempseyは各コアがハイパースレッディングに対応しているため、1CPUパッケージで2CPUコア、4論理CPUを実現できる。それが2つ搭載されているので、論理CPU数は合計で8。WindowsのCPUパフォーマンスメーターも、8つのCPUが動作していることを示す8つのグラフが同時に表示されていた。

|

| |

|---|---|---|

| 今回のデモの主役?を務めたDempseyのパッケージ。2つのダイを1パッケージに載せたデュアルダイ構成である | Dempseyを実際に動作させるデモを実演したデモ機(右) |

|

|---|

| 2つのDempseyによるデュアルプロセッサーシステムでWindowsを動作させている。写真ではやや分かりにくいが、8つの論理CPUが同時に動作し、負荷を割り振っている様子が分かる |

インテルCPUの2005年以降のロードマップも、改めて示された。内容自体は2004年後半から変わっていないが、すでに製品が出荷されているデスクトップパソコン向けのPentium D系列だけでなく、2006年にはIA-64サーバーからモバイルまで、全分野でデュアルコアCPUが登場する。平野氏は2006年には、デスクトップやモバイル向けCPU出荷の70%が、またサーバー向けでは85%がデュアルコアCPUになるとの予測を披露した。さらに、これらデュアルコアCPUを活用するアプリケーション開発を促進すべく、インテル製のソフトウェア開発ツールによるサポートも継続して行ない、近々同社のC++やFortran用コンパイラーが、新しいバージョン“9”へとアップグレードされるとの予定を述べた。

|

|---|

| インテルCPUの2006年以降までのロードマップ。水色の部分がデュアルコアCPUで、2006年には全セグメントに投入される |

講演の最後では、HPC分野向けのサーバー/ワークステーション(株)エッチ・アイ・ティー(HIT)代表取締役社長の英(はなぶさ)憲悦氏が登壇。同社によるPentium D 840-3.20GHzのテスト結果を披露し、スーパーコンピューターの計算速度世界ランキング“Top 500”でも使用されているベンチマークテスト“Linpack 1000”で10GFLOPS(浮動小数点演算を100億回/秒実行)を記録するなど、非常に優れたパフォーマンスを発揮しているとして、インテルのデュアルコアCPUへの期待を示した。

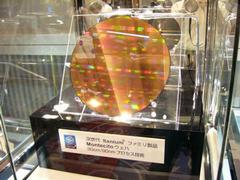

ショーケース会場には、開発中のデュアルコアCPUのパッケージなど、なかなか平素は目にする機会の少ない物が展示されていて、来場者の注目を集めていた。

|

| |

|---|---|---|

| Montecitoのダイを取る90nmプロセス/300mmサイズウエハー | Pentium Dを搭載するノードを4枚収納可能な、HITのHPCクラスター製品。1台で最大8CPUコアとなる | |

|

| |

| Montecitoを搭載して4論理コアのデモを披露していたサーバーのデモ機 | 左写真のCPU部分。CAUTIONの文字があるヒートシンクの真下がCPU。右はCPUへの電力供給部 |