シンガポールを拠点とする半導体製造のファウンドリー、チャータード・セミコンダクター・マニュファクチャリング(Charterd Semiconductor Manufacturing)社は15日、都内で記者会見を開き、現在取り組んでいる65nmプロセス技術の最新動向に関して説明した。

同社は2003年の第1四半期に米IBM社と90nm/65nmプロセスの共同開発と相互製造契約の締結を発表した。その後、独インフィニオン・テクノロジーズ社、韓国サムスン電子社なども65nmプロセスの共同開発に参加。今年1月には、米IBMとの間の技術開発計画を45nmプロセスまで延長することになった。

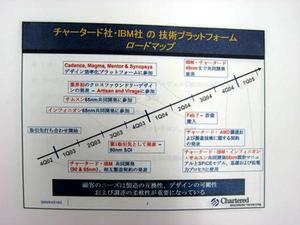

|

|---|

| チャータードとIBMの技術プラットフォームロードマップ |

同社の65nmプロセスは、ポリシリコン1層、金属配線層4~9層で、すべてCu(銅)配線となっており、トランジスターゲートには従来のコバルトシリサイド(CoSi2)に対してニッケルシリサイド(NiSi)が利用される。すでに65nm総合設計マニュアルや回路解析シミュレーション用のSPICEモデルなどを提供しており、2005年第4四半期に300nmウエハー対応の“Fab 7”で、試作用の“マルチプロジェクトウエハー”の生産,2006年にはパイロット生産を行なう計画である。なお、同社のトランジスターには、通常/低電力/高性能の3種類があるが、メーカーの需要などを考慮して製品が実際に出てくるのは低電力が2006年第3四半期と先行。続いて通常が第4四半期ごろに投入される予定。

|

|---|

| チャータード・セミコンダクターのジョン・マーティン氏 |

会見に出席した同社副社長ストラテジック・アライアンス・アンド・パートナーシップ担当のジョン・マーティン(John Martin)博士は、90nmプロセスから65nmプロセスに移行に関する技術的なチャレンジとして、リソグラフィーの問題、縦横のトランジスターのスケーリングの問題、そして、コバルトシリサイドからニッケルシリサイドへの材料の変化などを挙げた。また、「45nmプロセスの開発に関してもすでに始めている」と述べた。同席した米IBMフィールド・エグゼクティブ、システムソリューションのウォルター・F・ラング博士(Walter F. Lange)博士は、マーティン氏の発言を受けて「しかしながら、90nmで重要な技術は培われているので、それほど大騒ぎするほどではない」とフォローした。