【ISSCC 2005 Vol.6】“低消費電力でハイパフォーマンス”がキーワードとなったこれからのプロセッサー――ISSCC 2005セッションレポート

2005年02月14日 19時52分更新

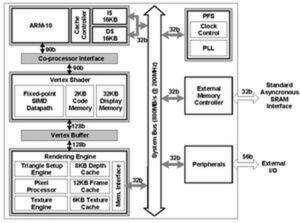

韓国科学技術研究所(KAIST:Korea Advanced Institute of Science & Technology)は、3G携帯電話への応用を想定した省電力性能に優れた3Dグラフィックスプロセッサー(GPU)のプロトタイプを、“A 50Mvertices/s Graphics Processor with Fixed-Point Programmable Vertex Shader for Mobile Applications”というセッションで発表した。

解像度の低い携帯電話やPDAといった携帯機器向けの組み込み用GPUを狙い、表示解像度が限定的であることに着目して、演算精度を固定小数点精度に割り切っているのが特徴だ。固定小数点の演算は基本的には整数演算器の組み合わせで実現できるため、ロジック回路規模の縮小にもつながり、ひいては消費電力の低下にも結びつく。

組み込み用GPU向けの標準グラフィックスAPI規格である“OpenGL ES”の次期バージョンでは、プログラマブルシェーダーの仕組みが導入されることがほぼ確定している。発表されたプロトタイプチップでも、プログラマブル頂点シェーダーの仕組みに対応するという。実装方法も少々ユニークで、コアプロセッサーとしてARM10ベースのRISCコアを採用し、これにコプロセッサー的に128bit(32bit×4)の固定小数点SIMDのプログラマブル頂点シェーダーを設けている。

|

|---|

| KAISTが発表した携帯機器向けGPUのブロックダイアグラム。固定小数点の128bit SIMD演算器を搭載しているのが特徴 |

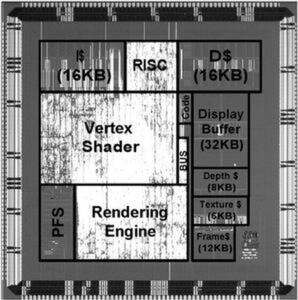

プロトタイプチップは0.18μm、6層CMOSプロセスにて製造され、トランジスター数は200万。米エヌビディア社(NVIDIA)の組み込み機器向けGPU“GoForce 3D”シリーズはトランジスター数600万なので、かなり小規模にまとまっていると言える。総消費電力はコア1.8V、I/O 3.3V、200MHz駆動時で155mW以下とのこと。

|

|---|

| プロトタイプチップのダイ写真。ダイサイズは4.8mm×4.8mm、チップサイズでも6.0mm×6.0mmと小さい |

性能は5000万頂点/秒で、GoForce 3Dの10倍というハイパフォーマンスだが、これは固定小数点系を採用したことによる恩恵が大きいと思われる。ピクセルレンダリングパフォーマンスは5000万ピクセル/秒、テクセルフィルレートは2億テクセル/秒。こちらはGoForce 3Dと同程度の性能だ。性能面ではパソコン向けGPUにはまったく及ばないが、携帯電話やPDAの低解像度画面がターゲットであることを考えれば必要十分と言えよう。ピクセル陰影処理はグローシェーディングどまりで、ピクセルごとの陰影処理には対応しない。割り切るところは割り切るスタンスだ。NVIDIAのGoForce 3DシリーズやフィンランドBitboys社のGシリーズが、パソコン用GPUのような高機能・多機能路線へ突き進んでいるのとは対照的だ。

|

|---|

| プロトタイプチップのスペック。小さな画面をターゲットとしているので、レンダリング最大解像度は512×512ドットまで |

なおKAISTは韓国サムスン電子と連名でもう一件、同様の組み込み機器向けGPUを発表したセッション“An SoC with 1.3Gtexels/s 3D Graphics Full Pipeline Engine for Consumer Applications”を行なっている。韓国勢の携帯機器分野への強い関心が窺い知れる。

インテル、MontecitoコアのItaniumの開発方針を説明

米インテル社は、IA-64ベースの64bit CPU“Itanium”シリーズの最新版である、コード名“Montecito”のItanium 2の開発経緯を発表するセッション“The Implementation of a 2-core Multi-Threaded Itanium Family Processor”を行なった。

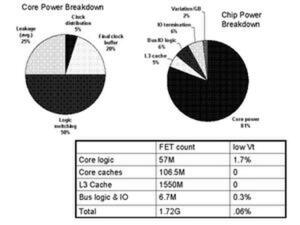

Montecitoは現行のItanium 2コア(Madison)相当を2つ、1チップに搭載したマルチコアCPUである。90nmプロセスルールで製造され、トランジスター数は実に17億2000万というモンスターCPUだ。ダイサイズは21.5mm×27.7mmの596mm2と、90nmプロセスのチップとしては破格に巨大である。1次キャッシュは命令16KB、データ16KB。2次キャッシュは命令1MB、データ256KB。3次キャッシュは12MBをそれぞれのコアに搭載するなど、キャッシュメモリーだけでも合計26MBを超える。

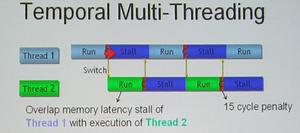

物理的なCPUコアは2基だが、各コアが論理CPUコアを2つ生成するため、ソフトウェア(OS)からは4基のCPUがあるように見える。この論理コアによるデュアルスレッドシステムは“Temporal Multi-Threading(TMT)”という名称がつけられている。1スレッドがシステムメモリーへのアクセスなどで待ち状態にある際に、スレッドを切り替えることで、物理コア内の演算リソースを効果的に活用するという仕組みとなっている。これは演算リソースの常時フル可動と、メモリーアクセスの際のレイテンシー隠蔽の両方の意味合いがある。同社によればTMTの効果により、メモリーアクセスのレイテンシーの状況によっては、15%~35%のパフォーマンス向上が得られると説明する。

|

|---|

| Temporal Multi-Threading(TMT)の動作概念図。メモリーアクセスでのストールが発生する度に、スレッドが切り替わる |

Montecitoの開発において最も注力されたのは、意外にも消費電力だったという。単純にMadisonコアを90nmプロセスを用いてシュリンクし、駆動電圧を下げてクロック周波数2.0GHzで駆動させたものをマルチコアCPU化してしまうと、消費電力はなんと300W近くになってしまうという。これはどうしても避けなければならないということで、新たな省電力技術が模索された。

まず基本となったのは、Montecitoコアを形成するトランジスターの最適化だ。具体的には、高速動作に向くがリーク電流の多いLow-Vtトランジスター(しきい電圧の低いトランジスター)をバスインターフェースやコアロジックの一部に限定し、Low-Vtの割合をCPU全体で0.06%にまで押さえ込んだという。これにより、結果として約28%の省電力が実現されたという。

|

|---|

| Low-Vtトランジスターの使用割合を示した図表。MontecitoにはLow-Vtトランジスターはほとんど使われていないことが分かる |

またプロセッサーの各ブロック単位に、負荷に応じてクロック周波数と駆動電圧を供給する仕組みも導入した。これにより、ある消費電力の範囲で最大性能を得るという仕組みも実現された。これがMontecitoコアの目玉の省電力機構“Foxton Technology”である。同社は今後ますます重要となってくるコンピューティングパラダイムである、“ワット当たりの性能”という要求に対するひとつの回答として、Montecitoを提供するとしてセッションを締めくくった。

|

| |

|---|---|---|

| チップ全体を省電力駆動するのではなく、チップ内でブロックごとに細かく電力制御を行なうのがFoxton Technologyの概念である | Foxton Technologyの動作概念図。温度センサー等の入力で駆動電圧を制御。電圧センサーはこれを入力として最適なクロックを出力する |