|

|---|

| 東北大学教授兼ザイキューブ取締役CTOの小柳光正氏 |

(株)ザイキューブは15日、東京・丸の内の丸ビルコンファレンススクエアで記者説明会を開催し、独自の“積層型3次元LSI”を開発した東北大学の小柳正光(こやなぎみつまさ)教授が同社の取締役CTO(最高技術責任者)に就任し、積層型3次元LSIの実用・量産化に向けた事業を本格始動すると発表した。同社は完成したLSI(ウエハーもしくはチップ)を積層する部分を担当する“セミファブレス”企業で、現在パートナー企業と事業に向けた話し合いを進めているという。2005年後半には同社の仙台開発センターに8インチの試作ラインを立ち上げ、2007年から2層の積層型3次元LSI、2008年に3層の積層型3次元LSIをそれぞれ量産化する計画がある、としている。

|

| |

|---|---|---|

| ザイキューブの代表取締役社長の盆小原 學氏(左)と常務取締役の上林和利氏 | 東北大学教授兼ザイキューブ取締役CTOの小柳光正氏(右)、東北大学教授 工学研究科長の井口泰孝氏(中央)、東北大学のVBL長の湯上浩雄氏 |

|

|---|

| 積層型3次元LSIの模式図 |

発表会には、ザイキューブの代表取締役社長の盆小原 學(ぼんこはらまなぶ)氏、常務取締役の上林和利(かみばやしかずとし)氏、東北大学教授兼ザイキューブ取締役CTOの小柳光正氏、東北大学教授 工学研究科長の井口泰孝(いぐちやすたか)氏、東北大学のVBL(ベンチャービジネスラボラトリー)長の湯上浩雄(ゆがみひろお)氏らが出席し、産学協同事業設立の経緯や積層型3次元LSIの詳細などを説明した。

|

| |

|---|---|---|

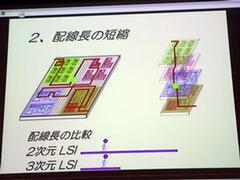

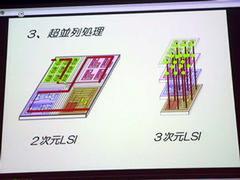

| チップ面積の減少 | 配線長の短縮 | |

|

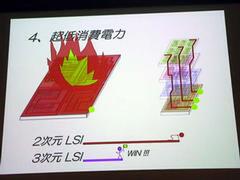

| |

| 並列処理の実現 | 超低消費電力の実現 | |

| 積層型3次元LSIのメリット | ||

小柳氏は開口一番、「米国のシリコンバレーなどを視察に行っているが、あちらは画期的な技術をすぐにベンチャービジネスとして立ち上げている。日本ではそれに比べると、産学協同といっても立ち遅れている感が否めない。3次元LSI技術の研究を始めて17年になるが、このほどようやくビジネス化にこぎつけた」と切り出し、続けて同氏が開発した積層型3次元LSI技術の詳細を説明した。

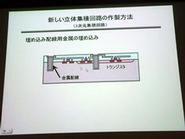

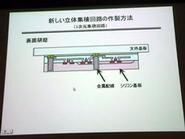

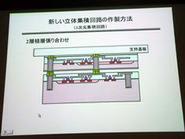

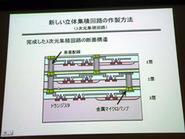

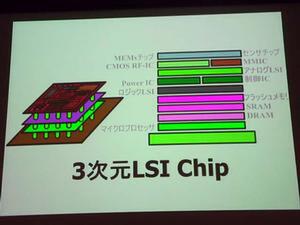

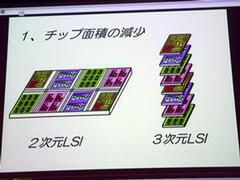

従来の同一平面上に回路を生成する2次元方式では、シリコンウエハーに必要な回路を個別に生成し、1つのチップを形成していた。小柳氏が開発した積層型3次元LSI技術は、こうして作成したウエハーもしくはパッケージ化したチップそのものに縦方向に貫通する配線を形成して重ね合わせることで、3次元LSIを生成するというもの。これにより、

- チップ面積の減少

- 配線長の短縮

- 並列処理

- 超低消費電力

などのメリットが得られると説明する。

|

|

| ||

|---|---|---|---|---|

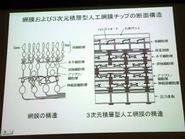

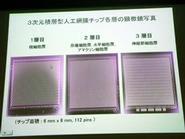

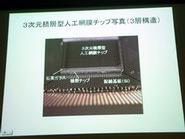

| 網膜の構造と3次元積層LSIを使った人口網膜の構造図 | 3次元積層で試作中という人工網膜チップの各層の顕微鏡写真 | 実際に3層の積層LSIで構成した人工網膜チップ | ||

| 積層型3次元LSIの応用例として人工網膜チップを紹介 | ||||

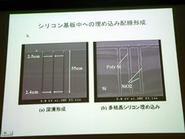

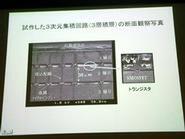

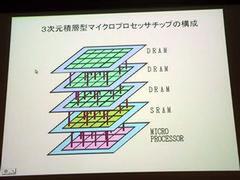

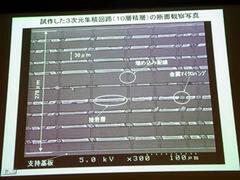

同様の積層回路設計としては、MCM(マルチチップモジュール)やCoC(チップオンチップ)といったワイヤーボンディングによる積層化技術が確立され、実用化されている。小柳氏の技術ではチップとしてパッケージ化する前のウエハーレベルで1~3μm程度の微細な貫通孔(最長55μm程度)をプラズマ技術で生成し、接合部分に金属マイクロバンプを形成、間に接着層(1μm)を設けて、10層程度までの積層が実現できるという。従来の積層回路技術に比べて、ウエハー同士の積層による薄型化、配線長の短縮が可能。例えば演算素子とSRAM/DRAMを積層することにより、動作クロックを引き上げることなく高速演算処理が可能になるため、排熱の問題もクリアできる(同氏の各種シミュレーションでは発生する熱も貫通孔を通じて排出されるとのこと)。

|

| |

|---|---|---|

| 同じく応用例としてDRAM/SRAMを混載したCPUを紹介 | 10層まで積層した試作も行なっているという |

活用例としては、上記の高速演算処理装置のほか、フォトダイオードの裏に水平細胞層/垂直細胞層/アマクリン細胞層/神経節細胞層などの各種回路を積層した“人口網膜チップ”も実現できると説明する。

|

|

| ||

|---|---|---|---|---|

| 3次元積層LSIの実現に必要なザイキューブの独自技術 | ザイキューブの掲げるビジネスモデル | ザイキューブの掲げる技術開発/製品化へのロードマップ | ||

| ザイキューブの持つ技術とビジネスモデル | ||||

続いて盆小原氏が、まずザイキューブの社名の由来を紹介した。それによると、“ザイ(Zy)”はバイオテクノロジーや医療系を、“キューブ(Cube)”は3次元を意味しており、3次元積層技術をこうした分野に応用していきたい、という姿勢を示したものだという。また、「肝になる技術は、微細な貫通孔と配線加工、および1μm以下という重ね合わせの精度で、ザイキューブでは重ね合わせる基板/ウエハーの生成は行なわず積層部分のみをビジネスにする。具体的には、デバイス設計や装置設計、試作・少数生産などを行なう。これによる投資コストが最小限に抑えられると説明している。また、当初はSiP(システムインパッケージ)やセンサーデバイスなどを手がけ、その後にメモリー混載や高性能LSIなど各種応用分野に進出したい」と同社の事業戦略について語った。

|

|

| ||

|---|---|---|---|---|

| 3次元積層型LSIの試作品と従来の2次元回路の比較 | 積層型LSIの概念をブロックで示したモデル | いくつかの試作品も展示された | ||

| 会場に展示された積層型3次元集積回路の試作品 | ||||