インテル(株)は12日、京都で14日まで開催中のVLSIシンポジウム“2003 Symposia of VLSI Technology and Circuits”に合わせ、東京と京都の2ヵ所でゲート長30nm(ナノ・メートル)の“トライ・ゲート・トランジスタ”やCMOS無線技術などの詳細発表を行なった。

|

|---|

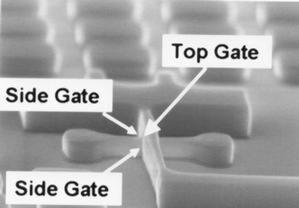

| “トライ・ゲート・トランジスタ”。Top Gate、Side Gate3ヵ所を電流が流れる |

米インテルのSenior Fellow,Technology and Manufacturing Group, and director, Process ArchitectureのMark Bohr(マーク・ボア)氏がゲート長30nm(ナノメートル)の“トライ・ゲート・トランジスタ”が研究段階から開発段階に移行したと発表した。同社では2002年に60nm(ナノメートル)のトライ・ゲート・トランジスタ開発を発表しているが、それから約1年でゲート長を半分に縮小することに成功したことになる。

従来のプレーナー型ではトランジスターゲートの上面にしか電気信号を流せなかったが、“トライ・ゲート・トランジスタ”ではゲートの上面のほかに両側面に電流を流せるため電気信号が通る領域を3倍にすることが可能で、プロセス技術が細分化されても供給電流を増加できる、シリコンの厚さのコントロールに関してプレーナー型よりも厳密にしなくて済むため量産に向いている、リーク電流(漏れ電流)を減少することができるなどのメリットがある。Bohr氏は「トライ・ゲート構造によってDrive Current(駆動電流)とOff Current(オフ電流)の比が非常によくなります。これは将来登場するハイパフォーマンスプロッセッサーにとって重要な側面です」と述べた。同社では2007年に実用化を目指す45nmのプロセスでこのトライ・ゲート・トランジスタの技術を搭載したいと考えている。

また、Director,Communications Circuits ResearchのKrishnamurthy Soumyanath氏がCMOS無線技術について解説。CMOS無線技術に関しては、9日にインテルフェロー兼コーポレート技術本部コミュニケーション&インターコネクト・ラボ ディレクタのケビン・C・カーン(Kevin C. Kahn)氏が記者発表を行なっているが、今回はより詳細な説明が行われた。 氏は「これまでの無線デバイスは大変複雑でチューニングが難しかった。そのため量産には耐えられないというのが現状だったが、我々はローコストでしかも複数のバンド幅を運用できる機構を目指している」と話した。そのために研究しているのが、様々なコンポーネントをデジタルCMOSに組み込んでいくというものだ。

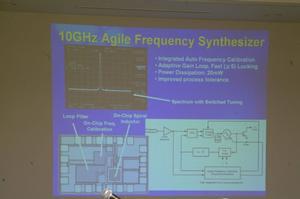

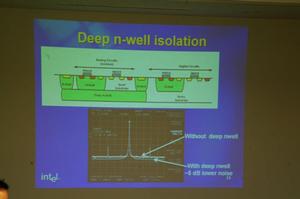

まず無線の心臓部であるシンセサイザーについて説明を行ない、10GHz帯のシンセサイザーを使って全ての帯域幅に合わせることが可能な“10GHz Agile Frequency Synthesizer”について紹介した。「これまで発表されたシンセサイザーを見てますとインダクターが外に置かれていることが多い。しかし、私どもは完全に回路に統合しています」とし、そのスペクトラムと回路図を示した。これで分かるのは、スペクトラムの線がきれいで正確であることだ。「どんな無線でもピークから多少幅がでるものですが、私どものシンセサイザーは非常にピュアなものとなっている」と自信を見せた。また、さまざまなメーカーが耐ノイズ性を高めるために、アナログ回路に“DeepーN-Well”を使っているが、本当にこれが必要かどうか、コストパフォーマンスを計った上で判断したいとコメントした。

|

|---|

| インダクターを統合したシンセサイザーの回路図(下)とスペクトラム(上) |

|

|---|

| ノイズ低減のためにアナログ回路に使われている“DeepーN-Well”。下の曲線は“DeepーN-Well”を使った場合と、使わなかった場合のノイズ波形。“DeepーN-Well”を使った場合は5dB低下している |

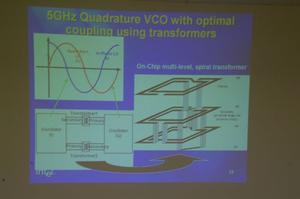

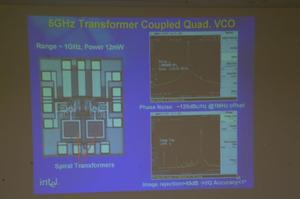

さらに、これらシンセサイザーの中核を担うVCO(Voltage Controlled Oscllator)についても言及。「シンセサイザーの精度はVCOのスペクトラム上の精度に依存している。したがって良いVCOを確実に使う必要がある」と話した。VCOではI値とQ値といった2つの信号値を使うが、これまでこの2つを結合するのにトランジスタを使用していた。しかし、これではどうしても精度が落ちてしまうとして、同社ではトランスフォーマーで結合したという。これにより、ノイズがほとんどのらなくなっているという結果が示された。また、“5GHz Transformer coupled VCO”の回路画面とノイズ・精度の測定結果を示しながら、「位相差の精度に関しては±2度くらいの精度が求められるのが一般的だが、私どもは1度未満に収めている。これによってデータ転送速度がアップし、ビットレートも改善されている」とした。具体的な数値は示さなかった。

|

|---|

| 2つのVCO(IとQ)をトランスフォーマーで結合しているとする図。右の図は6層で構成されいることを示す |

|

|---|

| トランスフォーマーを搭載した回路図と性能測定結果 |

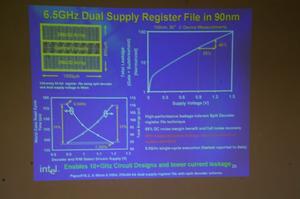

このほか、インテルのR&Dが研究していることとして漏れ電流対策が挙げられた。ここで紹介されたのは“6.5GHz Dual Supply Register File(90nm)”。「マイクロプロセッサーではいろんなところにレジスターファイルが使われており計算結果が書き込まれるわけですが、ここで漏れ電流をなるべく少なくする必要があります。レジスターファイルのスピードは絶対に落としてはいけないのです」と話し、1.2Vと0.9Vの供給電圧で46%の漏れ電流を削減したことが示された。また、ALU(整数演算ユニット)の代わりに専用のハードウェアを採用し、特にワイヤレスコミュンケーションに生かしていけないかを研究中であることが紹介された。現在、DSP Multiplierを使い1GHzで今まで最高のパフォーマンス(MIPS/W)を達成しているという。特に22mWという低電圧で達成していることも強調した。「消費電力を抑えために、高周波数、高スループットで使うことも可能」であると話した。

|

|---|

| “6.5GHz Dual Supply Register File(90nm)”。46%の漏れ電流を削減している |