続いて城取締役は、インテルの半導体製造戦略について説明した。同社は自己の強みを一気に大量生産を可能にする“製造能力”、市場・技術の変化に即座に反応する“敏捷性”とその業務遂行能力にあるとしている。

|

|---|

| インテルが進めている0.13μmプロセス技術の導入。2002年には6つのファブで生産が始まる |

0.13μmプロセスへの投資を継続

インテルは2001年第1四半期に0.13μmプロセス技術による半導体量産を開始し、これまでに4つのファブを0.13μmプロセスに移行したが、さらに2002年に300mmウエハーで製造する2つのファブを0.13μmプロセスに移行し、計6ファブという他社を圧倒する製造体制を敷くという。

|

|---|

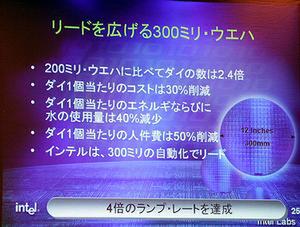

| 0.13μmプロセス導入によるメリット |

|

|---|

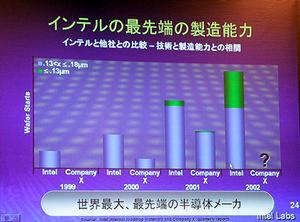

| “Company X”とインテルの製造能力の比較 |

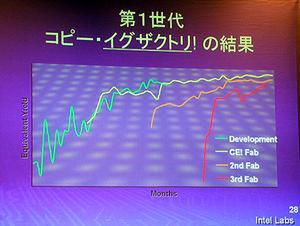

インテルは新しい製造技術を導入する際に、技術開発終了後はパイロットライン(量産の試験をする製造ライン)を経ることなく、すぐに大量生産ラインに移し、そこで製造を行なうようにしているという。そして、そのラインで十分なイールド(歩留まり)が得られるようになると、その生産ラインと全く同じ生産ラインをほかの工場に用意して生産するという“コピー・イグザクトリ!”という手法を行なっている。このコピー・イグザクトリ!によって、2番目以降の工場では、最初から十分にノウハウのたまった製造ラインによって、新たな製造ラインを用意するよりも早く、高い歩留まりの生産が開始できるとしている。

|

|---|

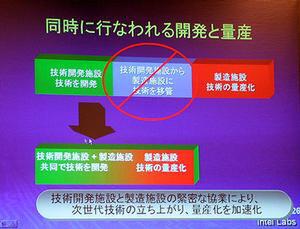

| 量産までの期間短縮を狙うインテルの戦略 |

|

|---|

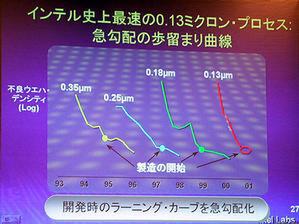

| プロセスルールが進むにつれて、歩留まりの向上がより早くなっている |

|

|---|

| “コピー・イグザクトリ!”と、通常のファブのイールドの立ち上がりグラフ。“CE!”とあるのが、コピー・イグザクトリ!によって立ち上げたファブ |

さらに、テラヘルツ・トランジスター・アーキテクチャーのようなトランジスター技術以外にも、インターコネクト(チップ内の配線)技術、シリコンウエハーの露光技術、チップのパッケージング技術においても、開発投資を行ない、成果を上げているとした。

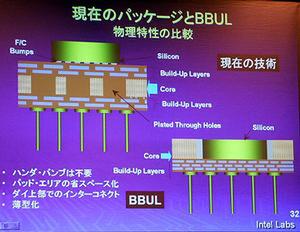

最後に城取締役は、米インテルが米国時間10月8日に発表した、10億個以上のトランジスターで20GHz動作するプロセッサーのためのパッケージング技術“BBUL(Bumpless Build-Up Layer)”について説明した。

|

|---|

| “BBUL”と従来のパッケージングの比較 |

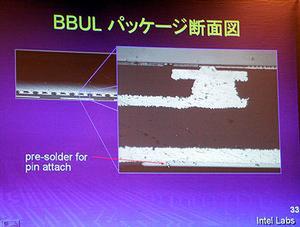

BBULは、現在のチップコアが“バンプ(Bump)”と呼ばれる球状のハンダを使って、パッケージ上の配線と接続しているのに対して、チップコアの端子部分に直接配線を形成していくという技術。パッケージの厚みが薄くなるため、配線が短くなり、高速化、低消費電力化が促進されるという。また、2つのプロセッサーコアを1つのパッケージに組み込むマルチチッププロセッサーや、プロセッサーコア以外のチップも1つのパッケージとする“システム・オン・パッケージ”も可能になるとしている。インテルでは、2006~7年にかけてのプロセッサーのパッケージングの1つとして採用するとしており、ノートパソコンやPDA、携帯電話などのプロセッサー向けに使われると見られる。

|

|---|

| BBULのパッケージ部分の断面拡大図。BBULのパッケージがいかに薄いかが分かる |