インテル(株)は12日、都内で記者発表会を開催し、米インテル社のインテル・フェロー兼技術・製造本部ロジック技術開発トランジスタ研究担当ディレクタのロバート・チャウ(Robert Chau)氏が、同社技術開発部門であるインテル研究所において、ゲート長が20nmと世界最小かつ最速のCMOSトランジスターを開発したと発表した(※1)。インテルは2000年12月に、当時最小最速となるゲート長30nmのトランジスターを発表しており、わずか半年で記録を更新したことになる。

※1 この発表は10、11日に京都のホテルで開催された、“シリコン・ナノエレクトロニクス・ワークショップ”で行なわれた。シリコン・ナノエレクトロニクス・ワークショップは、13日に開催される“VLSIシンポジウム”(主催:応用物理学会、IEEE)の関連プログラム。 |

|---|

| 米インテル、インテル・フェロー兼技術・製造本部ロジック技術開発トランジスタ研究担当ディレクタのロバート・チャウ氏。手に持っているのは12インチ(30cm)ウエハー |

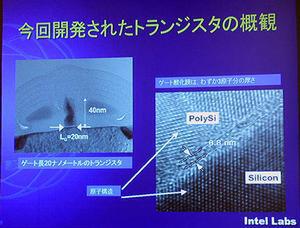

今回発表したゲート長20nmのトランジスターは、1秒間に1兆5000億回のスイッチングが可能で、ゲート長30nmのものに比べ、全体のサイズが30%縮小し、25%高速に動作するとしている。動作電圧は30nmのものが0.85Vに対して、20nmのものでは12%低い0.75Vとなっている。なお、ゲート酸化膜(SiO2)の厚みは0.8nm(原子3個分)で、30nmのものと同じ。

|

|---|

| ゲート長20nmのトランジスターの画像 |

|

|---|

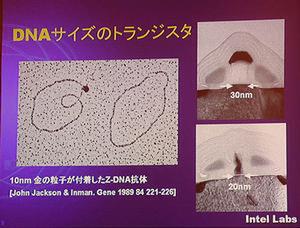

| 2000年12月に発表した、ゲート長30nmのトランジスター(右上)と、20nmのトランジスター(右下)の比較画像。左は大きさの比較のための画像で、大きさ10nmの金粒子が付着したDNA抗体 |

このトランジスターは、インテルが2007年に計画している“P1266"と呼ぶ0.045μmプロセス技術によって、ロジック製品として製造する予定。インテルは2年ごとに新しいプロセス技術を導入しており、『Xeon』プロセッサーの製造に使用している現行の0.13μmプロセスの3世代先のものになる。この0.045μmプロセス技術では、シリコンウエハーにトランジスターなどの回路を焼き付ける技術として、極紫外線(EUV)露光技術を採用する計画。

|

|---|

| インテルのプロセス技術のロードマップ。現在は0.18μmプロセスの“P858”から0.13μmプロセスの“Px60”への移行期。2000年12月の発表と合わせて予測すると、2005年には4億個のトランジスターを集積した10GHzのプロセッサーが登場、2007年には10億個のトランジスターを集積した20GHzのプロセッサーが登場する |

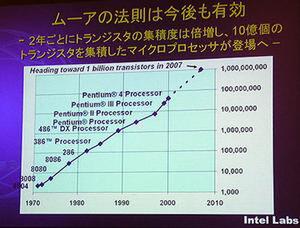

インテルは2007年に、10億個のトランジスターを集積し、1V以下の電圧で動作する、動作周波数20GHzのプロセッサーを開発する予定としている(現行のPentium 4は4200万個のトランジスター)。なお、ゲート長30nmのトランジスターの開発発表の際インテルは、4億個のトランジスターを搭載した、動作周波数10GHzのプロセッサーを今後5~10年以内に開発する予定としており、今回は時期がより具体的なものになっている。

発表会でチャウ氏は「今回の技術開発によって、“18ヵ月ごとにトランジスターの集積度が倍増する”という“ムーアの法則”が、少なくとも2010年まで基本的な障害が無く続くことが示された」と述べた。またインテル研究所で進められている研究の一部として、F2レーザー(波長157nm)およびEUVによる露光技術、低消費電力化と高速実行が可能な新しいトランジスター材料、高誘電率(High k)のゲート絶縁材料、高速実行と広いバンド幅が確保できる配線技術とパッケージング技術の開発が行なわれていると述べ、インテルの半導体技術が今後も業界をリードするとした。

|

|---|

| インテルプロセッサーにおけるトランジスター数の推移グラフ。ムーアの法則に従って、直線的に増加していることがわかる |

Q&Aでは、米IBM社が8日(米国時間)に発表した、シリコン素材による高速化技術ストレインド・シリコンに関しての質問が出たが、これに関してチャウ氏は「ストレインド・シリコンは10年以上前から大学や企業の研究機関で研究されている技術で、半導体開発者ならどういうものかわかっている。京都でIBMの開発者とも話したが、ゲート長が60nmの単独のNMOSトランジスターでの成果であり、CMOS、PMOS半導体で実現したものではない。ロジックなどの回路に対して有用な技術ではないと思う」と、プロセッサーへの応用に関しては否定的な見解を述べた。このストレインド・シリコンに関しては、インテル広報部も「インテルも研究をしたがプロセッサーには利用できないという結論に達した」としている。

またIBMはストレインド・シリコンの発表に際して、トランジスターの小型化は限界に達しつつあるとしていたが、京都のワークショップでチャウ氏はIBMの技術者とのパネルディスカッションで、今回発表したゲート長20nmのトランジスターの資料を示し、「まだしばらくはトランジスターの微細化は可能であると納得してもらった」と述べた。

インテルはこの20GHzプロセッサーによって、自然な会話によるコマンド入力や同時通訳、人の働いている様子からその仕事を片づけるために必要なことを予測する、といったことが可能になり、現在よりも遙かに使いやすく便利なコンピューターが実現できるとしている。パソコンが家庭のデジタル機器の中心にあり、生活を豊かにしてくれるというのがインテルの“ExtendedPC”のコンセプトだが、今回インテルが開発したトランジスターによるプロセッサーが登場したとき、それが現実になるのかもしれないと感じた。