インフィニオンテクノロジーズジャパン(株)の15日付けの発表によると、ドイツのインフィニオンテクノロジーズ社は現地時間の14日、同社のミュンヘン研究所“コーポレートリサーチラボ”が、現在のIC配線技術“ダマシン技術”を2011~2014年に登場する将来の世代のチップにも引き続き使用できることを実証したと発表した。

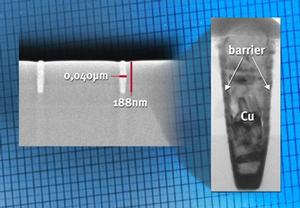

同社の研究者は、絶縁膜の溝の中に、線幅40~50n(ナノ)mの金属配線を製造することに成功した。このような微細な金属配線は、チップの中のトランジスター間を最短距離で電気接続するために使用される。さらに、電気抵抗も十分低いレベルであることが検証されたという。

|

|---|

| 線幅40~50nmの金属配線技術で試作したサンプル |

2011~2014年のチップ製造に必要なリソグラフィー装置は存在しないので、スペーサ技術を利用して、パターンを絶縁膜へ転写するためのマスクの開口部を狭めたという。この技術により、横方向の寸法に関して、最先端のリソグラフィー装置が実現できる線幅より狭い構造を製造することが可能になるという。

ダマシン技術では、ウエハー上の溝や穿孔を金属で埋め、その後に、埋め込み構造を覆うすべての余分な金属をCMP(化学機械研磨)法によって完全に除去する。実証用のシリコンウェハは、世界の有力な半導体メーカーをメンバーとするコンソーシアム“International SEMATECH”のクリーンルームで、線幅250nmの微細化技術用の標準半導体製造装置とプロセスを使用して処理加工された。

同研究所の今回の成果は、現在の配線技術が、半導体のための国際技術ロードマップ“ITRS”(International Technology Roadmap for Semiconductors)の最終年次である2014年まで使用可能であることを実証したという。