次世代チップセット『VIA Apollo DDR』は2001年前期に

台湾VIA Technologies、インテル対抗の高速内部バス接続技術を発表

2000年08月07日 22時13分更新

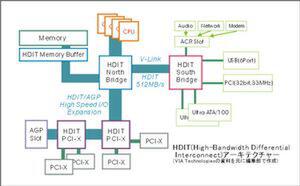

台湾のVIA Technologies社は7日(現地時間)、同社のPC向け次世代チップセット『VIA Apollo DDR』に搭載する、高速内部バス技術“HDIT(High-Bandwidth Differential Interconnect)アーキテクチャー”を発表した。HDIT対応チップセットは2001年前期の早いうちにサンプル出荷を開始する見込みという。

同社によれば、HDITアーキテクチャーの採用によって、DDR266メモリーインターフェース、AGP4X、同社の(※1)“V-Link Bus”などが統合されたSouth Bridgeチップを、デスクトップやモバイル用PC向けに提供できるとしている。また、ハイエンドのマルチプロセッサー搭載ワークステーションやサーバーに必要なスケーラビリティーも確保できるという。

※1 VIA Technologiesが新たに開発した、North BridgeとSouth Bridgeをつなぐためのバスの名称。最大で毎秒512MBのバンド幅を持つとしている。このNorth Bridgeチップはまた、DDR266メモリーコントローラーインターフェースとAGP4Xインターフェースを備え、最大4基までのプロセッサーをサポートする。メモリーインターフェースのバンド幅は、HDITメモリーバッファーの追加によってバス幅128bitで最大毎秒4.2GBに達するとしている。AGPポートへアクセスする際のバンド幅は最大毎秒2.1GB。さらに64bitの(※2)PCI-Xバスをサポートする、PCI-Xコンパニオンチップ(2チップ)も用意される。

※2 米国に本拠を置く業界団体“PCI(Peripheral Component Interconnect) SIG”が策定する、主にサーバーに向けた高速バス規格。現在のPCIバスが64bit、66MHzまでなのに対し、64bit、133MHzをサポートする仕様となっている。一方South Bridgeチップは、2チャンネルのUltra ATA/100コントローラー、8チャンネルのオーディオ、ソフトウェアモデム、6ポートのUSB、ネットワークインターフェースをサポートする。これは米インテル社の『815E』や『820E』に採用された、“ICH2”の仕様を踏襲しつつ、(※3)一部機能については上回るものとなっている。

※3 ICH2では、オーディオ機能は6チャンネル、USBは4ポートがサポートされている。North BridgeチップとSouth Bridgeチップ間は、V-Link Busにより、最大512MBのバンド幅で接続されるとしている。これは米インテルが『810』以降で採用している高速バス接続技術“インテルHUBアーキテクチャー”(バンド幅は毎秒266MB)を上回るものとなっている。

リリースによれば、同社プロダクトマーケティングディレクター、エリック・チャン(Eric Chang)氏は「32bitで33MHzのPCIバスは、1GHzプロセッサーを搭載するような先進的PCシステムの拡張や、North BridgeチップとSouth Bridgeチップを接続するためとしては、もはやまったく不十分だ。DDR SDRAMの利益を享受するためには、PCIバスがシステムのボトルネックになってしまっている」と、従来のアーキテクチャーでは、高速なメモリーやシステムが生かせないことを強調している。

HDITをサポートするVIA Apollo DDRチップセットは、ハイエンドデスクトップPC、ワークステーション、およびサーバー向けに、2001年前期の早いうちにサンプル出荷を開始するとしている。またこのチップセットは、インテルとAMD両社のプロセッサーをサポートするとしている。

|

|---|

| HDITアーキテクチャーを採用したチップセットの構成図 |