(株)富士通研究所は、FRAM(*1)用に強誘電体材料であるSBT(タンタル酸ビスマスストロンチウム:SrBi2Ta2O9)膜の低温形成技術を開発し、SBT膜を用いた68kbitFRAMと0.5μmCMOSロジックデバイスの混載チップの作成に成功したと発表した。

SBTを用いたFRAM(SBT-FRAM)は、データの書き換え回数が多く、低消費電力になると期待されている。従来は、SBT膜を形成する際に800度程度の高温処理が必要であり、SBT-RAMを混載したロジックデバイスを作成する際、トランジスタが損傷してしまう問題があった。今回、富士通研究所は、SBT膜の低温形成技術を開発し、その技術を用いてSBT-FRAMとCMOSロジックを混載したLSIを試作した。

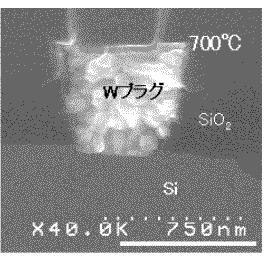

同社のSBT膜の低温形成技術は、塗布して形成するSBT膜の1回あたりの厚さを薄くし、700度で熱処理を行なうことによって可能としている。1回ごとに塗布形成するSBTを薄膜化することで結晶が緻密化し、低い結晶化温度でも特性のよいSBT膜を形成することができるという。

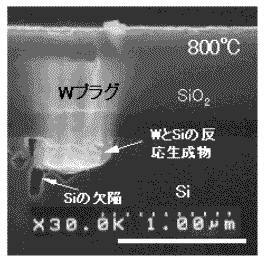

試作したデバイスは、0.5μルールの68kbitSBT-FRAMとCMOSロジックを混載したLSIで、タングステンプラグとシリコン基板による欠陥はなく、FRAM部とロジック部がともに正常に動作することを確認したという。

|

|---|

| 従来方法(800度)によるSBT膜形成後の回路 |

|

|---|

| 新規方法(700度)によるSBT膜形成後の回路 |

注1)FRAM(Ferroelectric RAM/FeRAM:強誘電体メモリー半導体):強誘電体の残留分極を利用した新しい不揮発メモリー。データの書き換え回数が多くかつ高速、消費電力が低いなどの特徴がある。登録商標は米Ramtron

International社が持つ。富士通はライセンス契約を結び、'96年からFRAMの開発を行なっている。