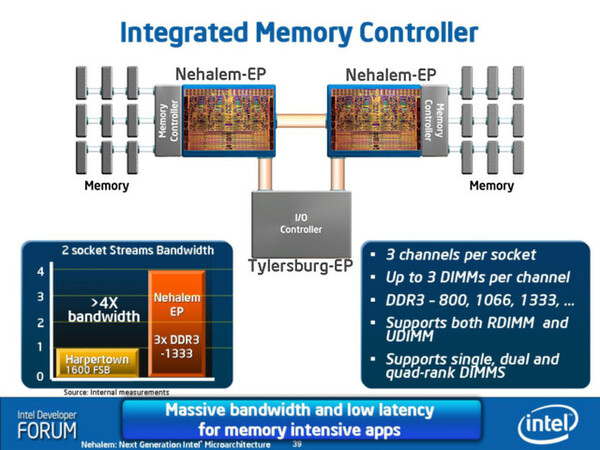

メモリーコントローラーをCPUに内蔵

Nehalemのもうひとつの大きな特徴は、メモリーコントローラーがCPUに内蔵されたことにある。PentiumからCore 2 Duoまで、インテルCPUはチップセット(MCHまたはノースブリッジ)でメモリーを制御していた。この方式は、メモリーの変更にチップセットで対応できるため、同じ設計のCPUで多様なメモリーに対応できる利点がある。

しかし、CPUからメモリーまでのルートが長くなるので、メモリーアクセスのレイテンシー(遅延)も長くなり、性能面ではデメリットがある。NehalemではCPU自身にメモリーコントローラーを内蔵したことにより、メモリーアクセスのレイテンシーは小さくなる。これはPC全体のパフォーマンスを大きく向上させる。

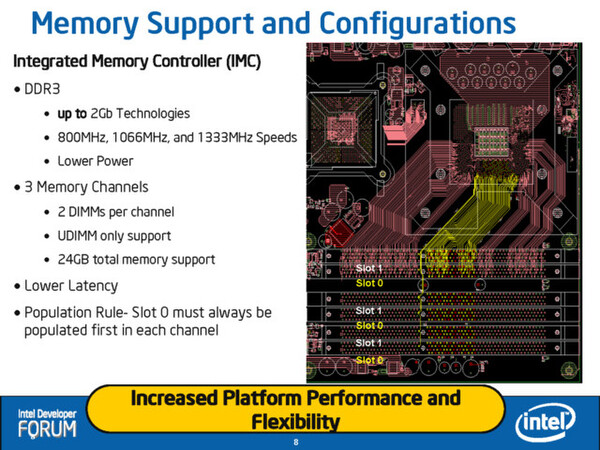

Nehalemでは、DDR3-800、1066、1333MHzメモリーをサポートしている(DDR2はサポートしない)。メモリー接続用のチャンネルは3チャンネル分サポートする。1チャンネルあたりのメモリースロットは2つで、計6枚のメモリーで最大24GBまで対応する。

Unbuffered DIMMに対応するか、Buffered DIMMのみ対応かは、Nehalemの種類によって異なるようだ。Nehalemのハイエンドデスクトップ向けCPU「Bloomfield」(ブルームフィールド)の説明では、Unbuffered対応と説明された。一方、サーバー&ワークステーション向けのNehalemは、BufferedとUnbufferedの両方が使用できるとしている。

CPUにメモリーコントローラーが内蔵されるということは、複数のCPUを搭載するシステムでは、それぞれのCPUごとにメモリーが搭載されることになる。つまり、メモリーアーキテクチャーがNUMA(ヌーマ、Non Uniform Memory Access)になる。なお、米AMD社のOpteronもNUMAアーキテクチャーを採用している。

NUMAに関する細かな説明は省くが、CPUごとにメインメモリーが分かれるため、OSはそれぞれのCPUに属するメモリーを参照する必要が出てくる。Windows VistaやWindows Server 2008は、OSがNUMAをサポートしている。だが、現在NUMAアーキテクチャーを採用しているシステムは、大規模なサーバーシステムばかりだ。Nehalemの登場により、2CPU以上を搭載するワークステーションやエントリーサーバーも、NUMAアーキテクチャー対応OSへと移行する必要が生じる。シングルCPUのパソコンは今までとは変わらない。多くのパソコンユーザーにとっては、NehalemだからといってNUMAアーキテクチャーを意識することはないだろう。

CPUにメモリーコントローラーが搭載されると、メモリーの世代移行も緩やかになるだろう。少なくとも2009年後半からリリースされるWestmereまでは、DDR3が主流として続くことになる。そのWestmereでは、32nmプロセスへの移行が重要課題になると考えると、Westmereで次世代のメモリーシステムへ移行する、というのも考えにくい。次々世代の「SandyBridge」(サンディブリッジ)までは、DDR3が使用されることになるだろう。

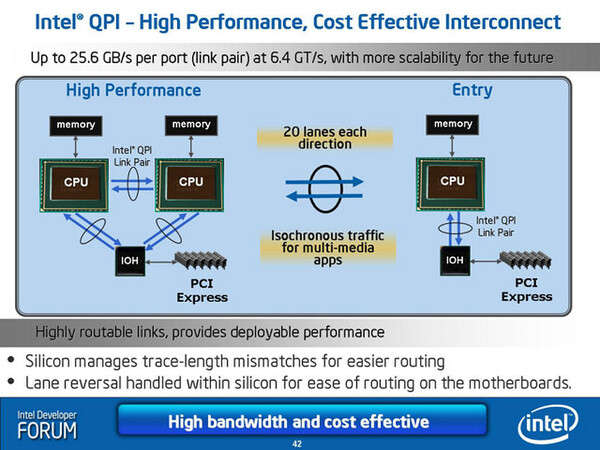

インターコネクトは「FSB」から「QPI」へ

NehalemではCPUとチップセット間のインターコネクトバスが、既存のシステムバス(FSB)から、新しい「QuickPath Interconnect」(以下QPI)に変更される。

QPIは、PCI Expressと同じようなポイントツーポイントのシリアルインターフェイスだ。上り下りそれぞれに20bitずつの帯域を持ち、25.6GB/秒のデータレートを実現している。

シングルCPUのNehalemシステムでは、CPUと「IOH」(I/O Hub、従来のMCHからメモリーコントローラーを除いたもの)が1組のQPIで接続される。ちなみにICHは残り、機能が向上した「ICH10」(後述)へと移行する。

2CPUを搭載するNehalemシステムでは、ひとつのCPUが2組以上のQPIをサポートする必要がある。1組はIOHとの通信を行ない、もう1組は片方のCPUとの通信を行なうわけだ。同様に、2CPU対応のIOHはQPIを2組サポートする必要がある。4CPU環境ともなると、それぞれのCPUにQPIが4組必要になる。NehalemではQPIの数で、パソコン向けとサーバー&ワークステーション向けを区別するのかもしれない。

CPUコアのマイクロアーキテクチャーは小幅な改良

NehalemのCPUコアのアーキテクチャー自体は、Penryn世代の「Coreマイクロアーキテクチャー」から小幅な改良に止まっている。

Penryn世代との大きな差は、64bitモードでのマクロフュージョンがサポートされたことだ。Penryn世代までのCoreマイクロアーキテクチャーでは、32bitモードではマクロフュージョンにより処理性能を上げていたが、64bitモードではサポートしていなかったため、パフォーマンスが向上しなかった。Nehalemで64bitモード時のマクロフュージョンがサポートされたので、64bit環境での処理性能向上が期待できる。

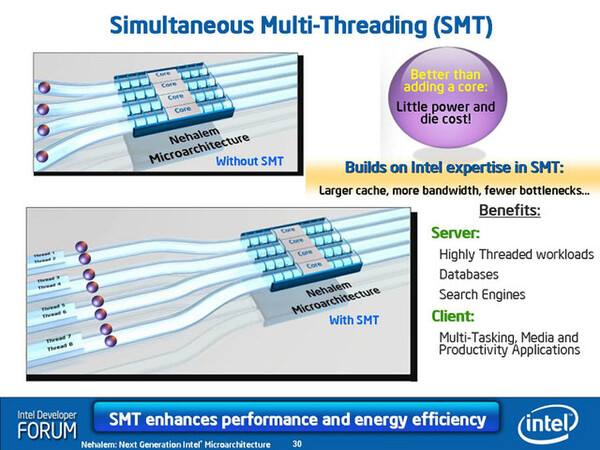

さらに、Pentium 4で採用されていた「Hyper-Threading Technology」(HT)と同じような、「SMT」(Simultaneous MultiThreading)が、Nehalemではサポートされた。これにより、ひとつのCPUコアを仮想的に2つのCPUコアとして動かすことができる。つまり、4コアのNehalem環境は、ソフトウェアからは8コアのプロセッサーとして動作する。

なお、NehalemのSMTがHTと名つけられていないのは、純粋にマーケティングの問題からだ。機能的には、HTとほとんど変わらない。

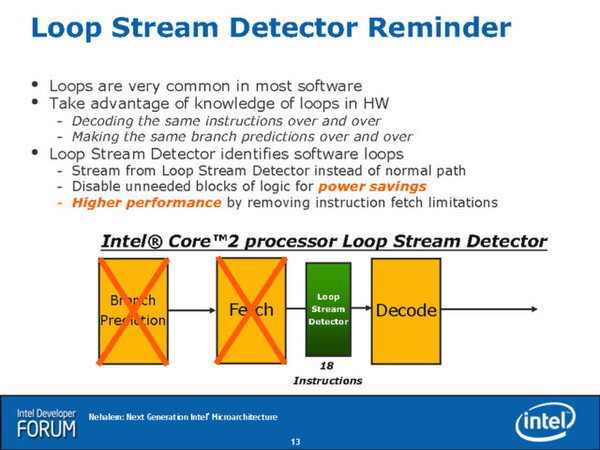

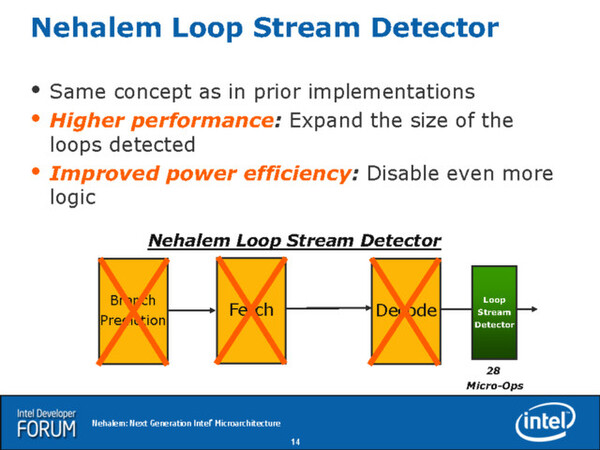

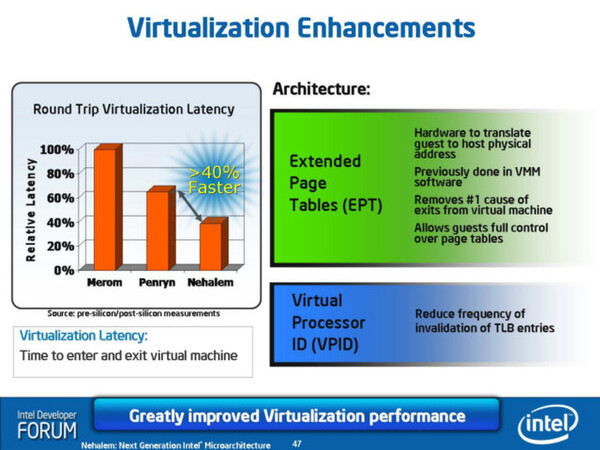

これ以外にも、分岐予測の機能強化されるほか、「Loop Stream Detector」(LSD)が改良され、ループを繰り返す命令群をすでにデコード後の部分で繰り返すことでパフォーマンスを向上させる。「Translation Lookaside Buffer」(TLB)を2階層化することで、メモリー操作を高速化する機能も導入される。さらに、ハードウェア仮想化を高速にする「Virtual Processor ID」(VPID)、「Extended Page Tables」(EPT)などの機能も追加されている。

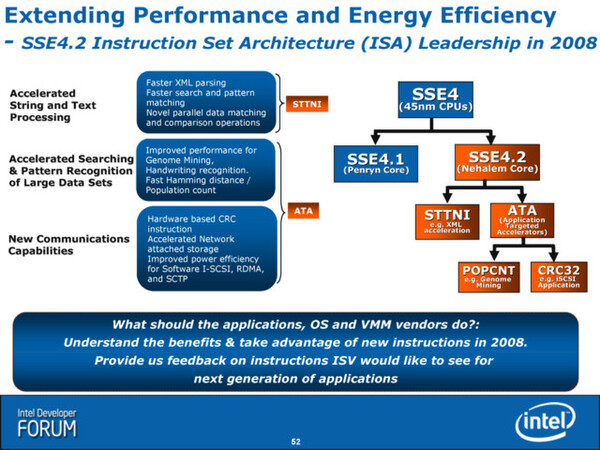

マルチメディア処理向け命令セットである「SSE」も、Penryn世代の「SSE4.1」から、Nehalem世代では「SSE4.2」に強化されている。SSE4.2では、SSE4.1から7つの命令セットが追加されている。XMLの解析を高速化する「STTNI」(String&Text New Instructions)、CRC32処理(iSCSIなどで使われているエラーチェック)、「POPCNT」(データマッチを高速に処理する命令)などが追加されている。特にCRC32やPOPCNTなどは具体的なターゲットを絞った高速化のための命令であるので、「Application Targeted Accelerators」(ATA)と呼ばれている。

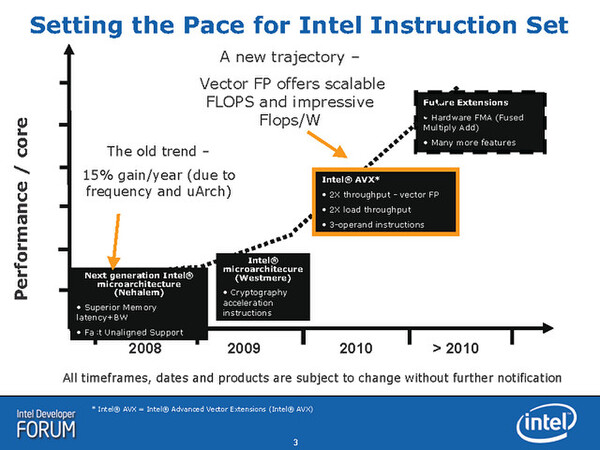

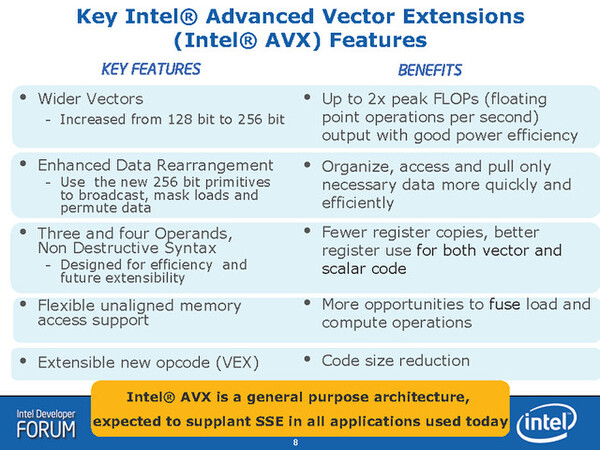

ただしSSEに関しては、SandyBridge世代で「Intel AVX」(Intel Advanced Vector Extensions)という命令セットが導入されるタイミングで、根本的に改良される。AVXでは演算幅を128bitから256bitに拡張する。さらに、今まで“屋上屋を重ねる”形で拡張されてきたSSEを根本的に見直し、スマートに整理するという。