ダイの構造から考えられる

3次キャッシュの大容量化

CPUダイが78mm2、I/Oダイが132mm2という面積をどう考えるかであるが、もともとのZenのダイ(210mm2)と比較するとかなり大きい、というのが筆者の偽らざる印象である。

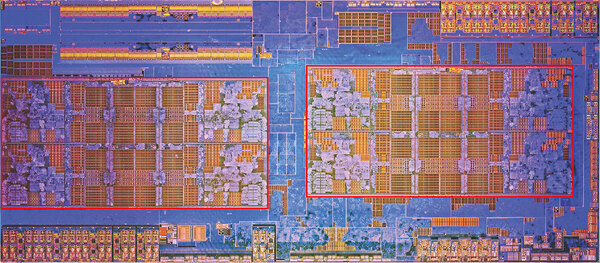

下の画像はZenのダイの内部であるが、赤く囲んだCCX(Core Compulex:CPUコアのクラスター)の面積はだいたい47.5mm2ほどになる。これが2つで95mm2という計算である。

連載484回でも示されているように、TSMCの7nmプロセスはラフに言ってGlobalfoundriesの14nmプロセスの倍のトランジスタ密度(配線密度と言っていないところが肝ではあるが、その話はおいておく)なので、このCCXの構造そのままに7nmに移行した場合、それこそ47.5mm2程度で収まらないとおかしいことになる。

実際にはFPUの帯域を倍増する)などの変更もあるため、もう少し大きくなるかもしれないが、それでも50mm2強といったところだろう。

このZen 2の構造の場合、CPU側のダイは8コア分のCCX+インフィニティ・ファブリックのPHYのみが搭載される構造になる。するとインフィニティ・ファブリックのPHYが27mm2も占めることになってしまう。いくらなんでもこれは大きすぎる。

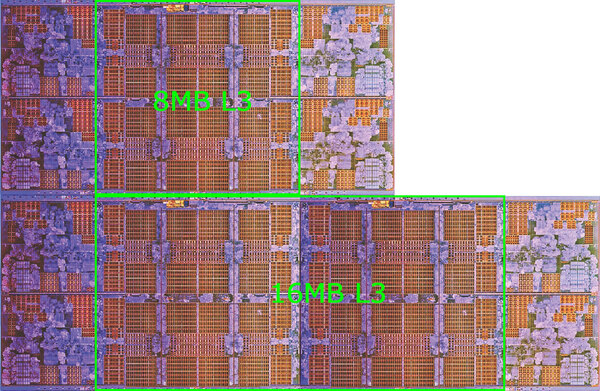

では他になにか拡張があり得るか? 1つ可能性としてあるのは、3次キャッシュの大容量化である。現在はCCXあたり8MB(つまりダイあたり16MB)になっているが、これを倍増したらどうなるか? というのが下の画像である。

この16MBの3次キャッシュ(つまりダイあたり32MB)の構成の場合、CCXあたりの面積は14nmで72.2mm2ほどになる。7nmを利用すれば、CCXが2つで72~73mm2というあたりになり、するとインフィニティ・ファブリックのPHYが5~6mm2という計算になる。

少なくともインフィニティ・ファブリックが27mm2を占めるというストーリーよりもこちらの方がはるかに現実味があるだろう。

なぜ3次キャッシュを倍増させるかといえば、FPUの256bit化への対応である。つまり1サイクルあたりが扱うデータの量がZen世代から倍増しており、これに向けてロード/ストアーユニットも256bit化されているわけだが、本来ならばこれにあわせてメモリーアクセスの帯域も倍増させないとメモリーがボトルネックになる。

ただこれを解消するためにはDDR4のチャネル数を倍増させないといけず、これは難しい。そこで解消はされないにしても緩和する方法が3次キャッシュの大容量化である。

AMDは公式には3次キャッシュの容量についてなにも言っていない(増やすとも増やさないとも言及していない)が、ダイサイズから考えるとけっこうありそうな気がする。

I/Oダイサイズの132mm2は

妥当な数値

ついでにI/Oダイについても話をしよう。先の計算では、14nm世代でCCXが1つあたり47.5mm2なので、CCXを2つ除いた残りの部分のダイサイズは115mm2程度になる。

Zen世代のダイになく、Zen 2世代のI/Oダイにあるものはインフィニティ・ファブリックのI/Fである。前述の3次キャッシュ倍増の試算が正しいとすれば、インフィニティ・ファブリックに要するダイ上のエリアサイズは7nmプロセスでだいたい5mm2程度。14nmで倍増するとしても10mm2ほどになる。

そうなると、I/Oダイにインフィニティ・ファブリックのI/Fを2つ搭載すると、合計のダイサイズは135mm2程度になる計算で、上に示したおおむね132mm2、という寸法にかなり近くなるかたちだ。

実際にはI/Oダイでは他にPCI Express Gen3→PCI Express Gen4への移行といった要件もあるが、こちらはダイサイズそのものが大きくなる要素はあまりなく、PHYの周辺だけドライバー部でトランジスタ数が多少増える程度であろう。

逆にZenの世代ではPCI Expressはインフィニティ・ファブリックと共用の形になっていたが、Zen 2ではPCI ExpressのPHYはPCI Expressのみなので(EPYC用のI/OダイはCCIXへの対応が必要だが、Ryzen向けにはCCIXのサポートはおそらくないだろう)、むしろエリアサイズが減っている可能性すらある。そう考えると、132mm2という寸法は妥当なのではないかと思う。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ