Zen 2はまずEPYC向けを投入

その後にRyzen向けをリリース

低速な周辺I/Oはともかく、メモリーコントローラーやPCIeなどは7nmで十分製造できる。それにもかかわらずこれらまで全部I/Oチップに統合したのは、マルチチップ構成における不均一さを解消するためと、さまざまなバリエーションの製品をこれで製造できることが理由と思われる。

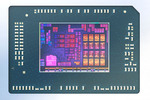

まずマルチチップ構成における不均一さとはなにか? 下の画像は従来のEPYCの構成だが、これだと例えばDie 1上で動いているスレッドは、Die 1に接続されているメモリーやPCIeには高速にアクセスできる反面、Die 2~4に接続されているメモリーやPCIeにはアクセスが遅くなる問題があった。

要するに、物理的にどこのダイ上で動いているかによって、おそろしくレイテンシーに差が出やすいということで、これが理由で性能が下がることがあった。

EPYCの話ではないが、今年10月にAMDはRyzen Master 1.5で、Ryzen Threadripper 2970WX/2990WX向けとなる“Dynamic Local Mode”を搭載した。

この効果は最新パーツ性能チェック第239回で「ねちっこく」説明されているのでご一読をお勧めするが、煎じ詰めればこれもコア毎に接続されているメモリーやPCIeに差があるから必要となる技術なわけだ。

Zen 2ベースのEPYCは、おそらく内部的には下図のような構成になっている。この構成ではすべてのダイからメモリーコントローラーやPCIeと均一のレイテンシーでアクセスできるようになるため、物理的にどこに接続されているかといった問題は発生しなくなるわけだ。

これにあわせてインフィニティー・ファブリック自身も次世代のものになった、という説明もあったがこちらは詳しくは不明である。帯域を更に拡張するとともに、レイテンシー削減に向けた手をさらに打っているものと思われる。

もう1つのラインナップであるが、この構成であればI/Oチップを変更するだけでさまざまな製品が作れるようになる。

連載470回で、AMDの関係者の談話(われわれが初代のRyzenやVegaで得た原則(Principal)は、サーバー向けとクライアント向けで同じダイを利用することで、最小限のコストで最大限の売上を獲得するというものだ)を紹介したが、Zen 2はまずはEPYC向けとして投入されるものの、その後はRyzen向けにも当然リリースされることになる。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ