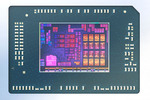

Zen 2ではコアの構成を大きく変更

さて、それよりも大きな話はコアの構成である。Zenコアの場合は1チップでSoC構成になっていた。つまりCPUコアとキャッシュのみならずメモリーコントローラー、PCIeとインフィニティー・ファブリック共用のI/O、それとチップセットまでが統合されていた。これがZen 2世代では大きく変更されることになった。

“7nm CPU Chiplets”は要するにCPU側のダイであって、こちらはCPUとキャッシュ(おそらく3次キャッシュまで)、それとインフィニティー・ファブリックしか搭載されていない。メモリーコントローラやPCIeを含むI/O全部はすべて14nm I/O DIE側に移動した形になる。

こうした構成になる理由は2つ考えられる。1つは7nmプロセス側の制約である。TSMCはハイスピードロジック向けのIPをN7向けに用意しており、これに加えてさまざまなEDAベンダーやIPパートナーがハイスピードI/OのIPを提供する形になるが、そもそも7nmでは駆動電圧が低いため、それこそUSB 1.1/2.0で必要とされる5VやI2C/SPI、SATAなどの3.3V系の信号を駆動するのは結構大変である。

それもあって、現時点ではこうした(相対的に)高電圧なI/Oに関してはそもそもIPの提供が遅れている。したがって、これをCPUコアの中に統合するのはタイミング的に難しい。そこで、I/O周りは外部のコンパニオンチップにまとめてしまい、CPUコアとの間を高速リンクでつなぐ、という方式はZen 2に限らずしばしば見かける手法である。

やや古い話になるが、中国HiSiliconは2014年にTSMCの16FF(16FF+ではない)を利用した、32コアのCortex-A57を搭載したサーバー向けSoCを開発しているが、この時も16FFを利用して製造されたのはCortex-A57のみで、周辺チップは28nmプロセスで製造され、TSMCのCoWoSを使ってつなぐという形になっている。今回AMDも周辺I/O周りを外出しにするのは、プロセス技術上必須だっただろう。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ