Sandy Bridge以降のCore iシリーズは

すべてRing Busを採用

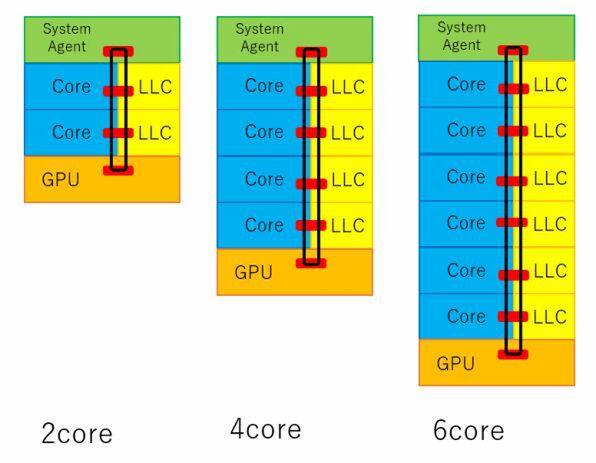

XeonではRing Busを廃した一方で、コンシューマー向けのCore iシリーズ(除くCore-X)については、Sandy Bridge以降Ivy Bridge、Haswell、Broadwell、SkyLake、KabyLake、CoffeeLakeではすべて、Ring Busを利用している。下図がその内部構造で、System AgentとGPUの間にCPU CoreとLLCを挟み込む形でどんどん数を増やしているのがわかる。

単純にコアを増減させるだけなら、Ring Busは共有バスと同じ程度に簡単に変更できるのが大きなメリットというわけだ。 ちなみにインテルのSkylake-SPやCore iシリーズで採用されているのは、いわば「擬似二重Ring」構成である。

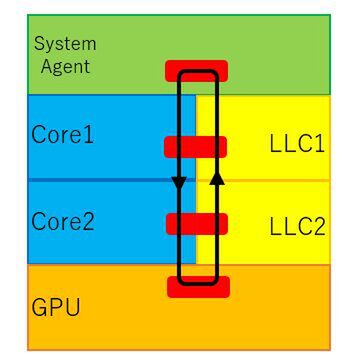

下図は2コア製品の拡大図である。中央の黒い輪がRing Busで、これは一方向にしかデータが流れない。ただし、Ring Stop(赤い部分)に関しては、2つのコアは上りと下りの2方向につながっている。

Core iシリーズ2コア製品の拡大図

たとえばCore 1からみると、Core 2あるいはGPUに通信したい場合は下り方向に、System Agentに通信したい場合は上り方向にデータを流せば、最小のレイテンシーでデータが送られるというわけだ。

一見良さそうに見えるが、この方式では両端にあるGPUとSystem Agentは事実上Ring Stopが1つしかないわけで、たとえばCore 1とGPU、あるいはCore 2とSystem Agentの通信は短縮できない。もっと問題なのはGPUとSystem Agentの通信で、これはCPUコアの数だけレイテンシーが増えることになる。

この擬似二重Ring方式は、CPUの数が6個くらいが現実問題としては限界に近い(8個も実現できるとは思うが、やや性能へのインパクトがありそうだ)。したがって今後メインストリーム向けに8コアが普通に登場するようになると、多少構成が変わるかもしれない。

ただ4コア以下に関してはきわめて合理的な方法であって、拡張性をある程度無視できるなら最適な方法である。インテルがRing Busを使い続けるのはこのあたりが理由であろうし、逆にAMDはZenで当初から8コアを想定していたので、Ring Busは最初から考慮に入ってなかった、というあたりではないかと思われる。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ