低コスト向けの22FFLを

2018年中ばごろに市場投入

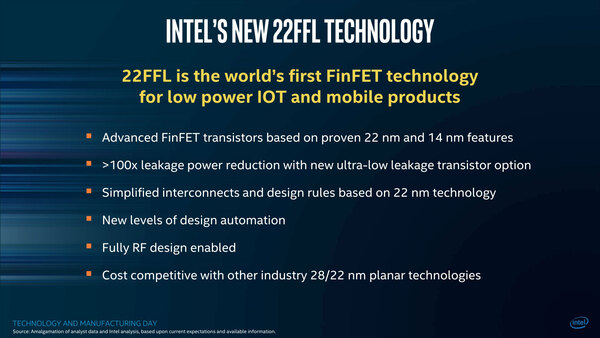

最後に、この3月に新しく発表された22FFLについて触れておく。これはTSMCの16FFC/12FFCやサムスンの14LPC/14LPU、あるいはGlobalFoundriesの22FDX/12FDXと同じような、低コスト向けプロセスである。

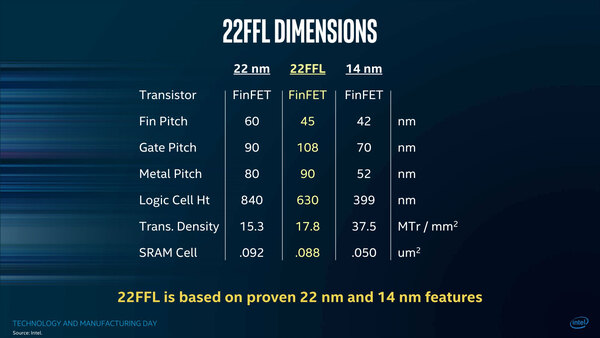

数値を見てみると、Fin Pitchこそ大幅に削減されているが、Gate PitchやMetal Pitchはむしろ大型化しており、Cellの高さを削減することで密度をやや高めた、といった構成になっている。

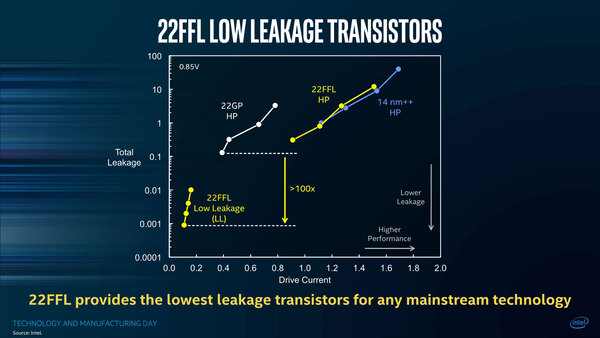

ただGate Pitchを大幅に増やしたことで、Low Leakage動作にすると極端にリーク電流を減らせるとしており、こちらはIoT機器向けとなり、逆に一般的な用途は14nm++と同等としている。

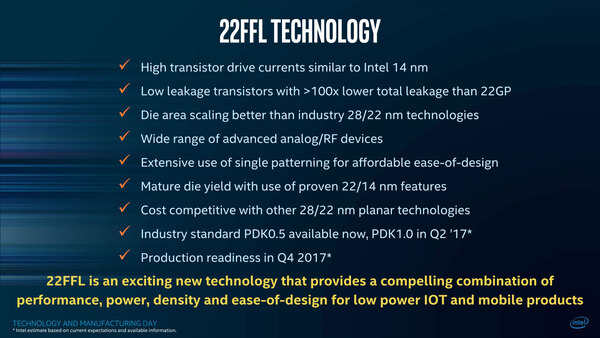

こちらは今年第4四半期から量産可能ということになっており、早ければ来年中旬には製品が市場投入できることになる。もっともそれを誰が使うか? というのが次の問題である。

インテルの製品で言えば、Intel 400シリーズチップセットや、次世代のThunderbolt 3コントローラー、10GBase-Tコントローラーなどには、ちょうど手ごろかもしれない。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ